## COMPUTER SYSTEM A RCHITECTURE THIRD EDITION

# Carnegie Mellon University

M. Morris Mano

Chap. 4: Register Transfer and Microoperations

- Register Transfer Language, Register Transfer

- Bus and Memory Transfers

- Arithmetic Microoperations

- Logic Microoperations, Shift Microoperations

- Arithmetic Logic Shift Unit

Chap. 5: Basic Computer Organization and Design

- Instruction Codes,

Computer Registers

- Computer Instructions,

Timing and Control

- Instruction Cycle,

- Memory Reference Instructions

- Input-Output and Interrupt

- Complete Computer Description

- Design of Basic Computer

- Design of Accumulator Logic

Chap. 6: Programming the Basic Computer

- Machine Language,

Assembly Language

- Assembler, Program Loops

- Programming Arithmetic and Logic Operations

- Subroutines, Input-Output Programming

**Chap. 7: Microprogrammed Control**

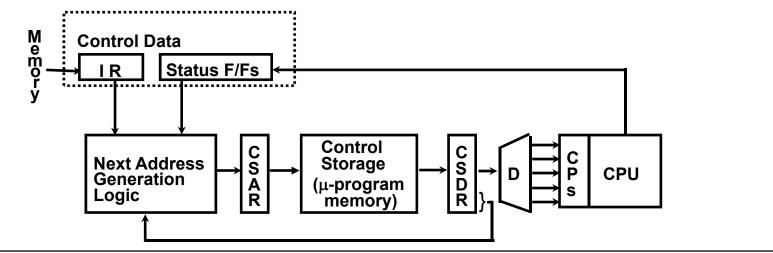

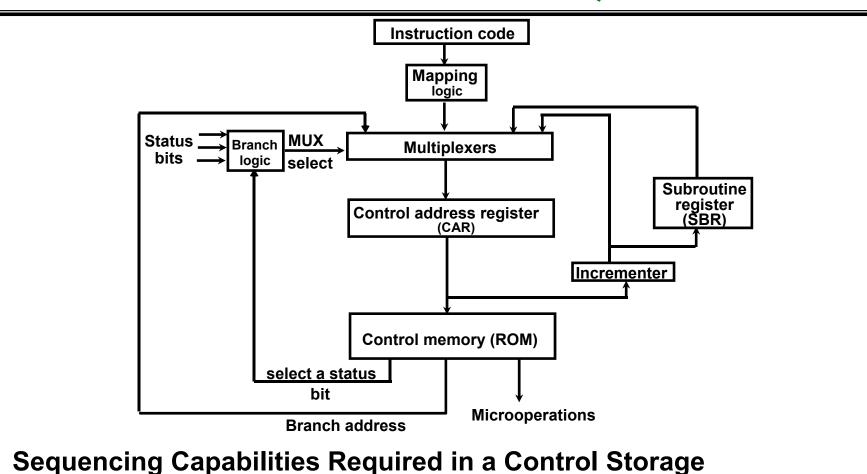

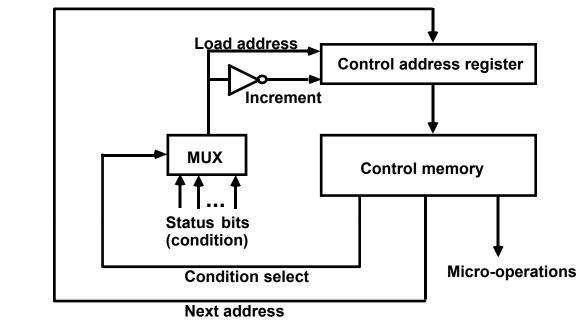

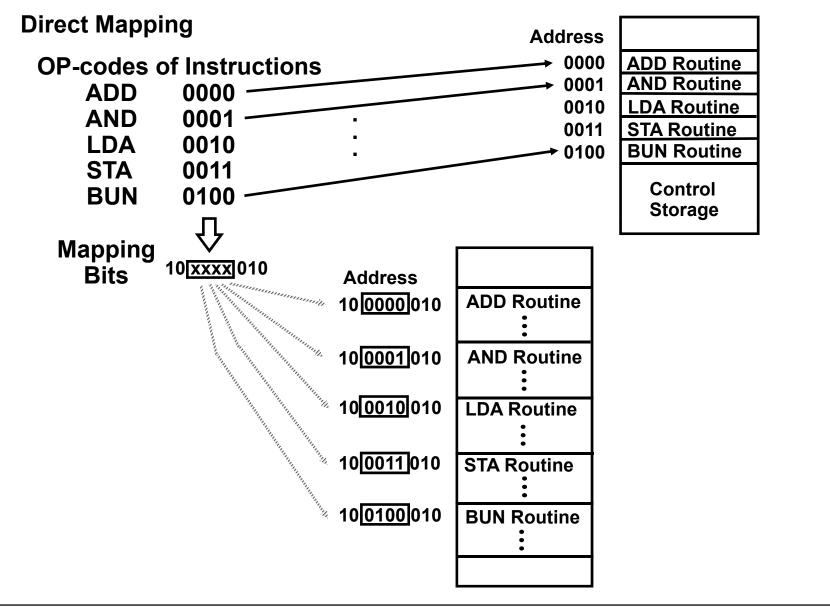

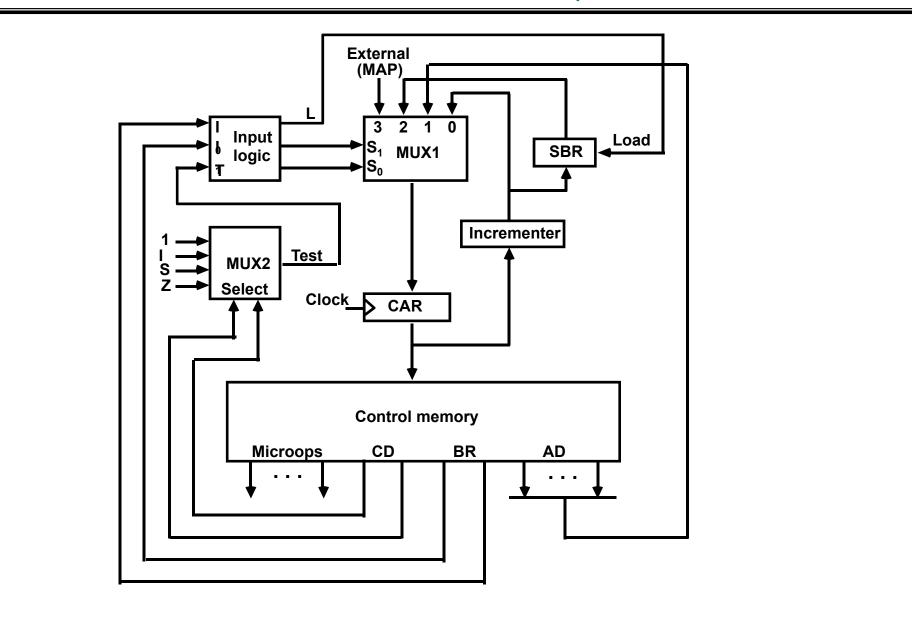

- Control Memory, Sequencing Microinstructions

- Microprogram Example,

Design of Control Unit

- Microinstruction Format

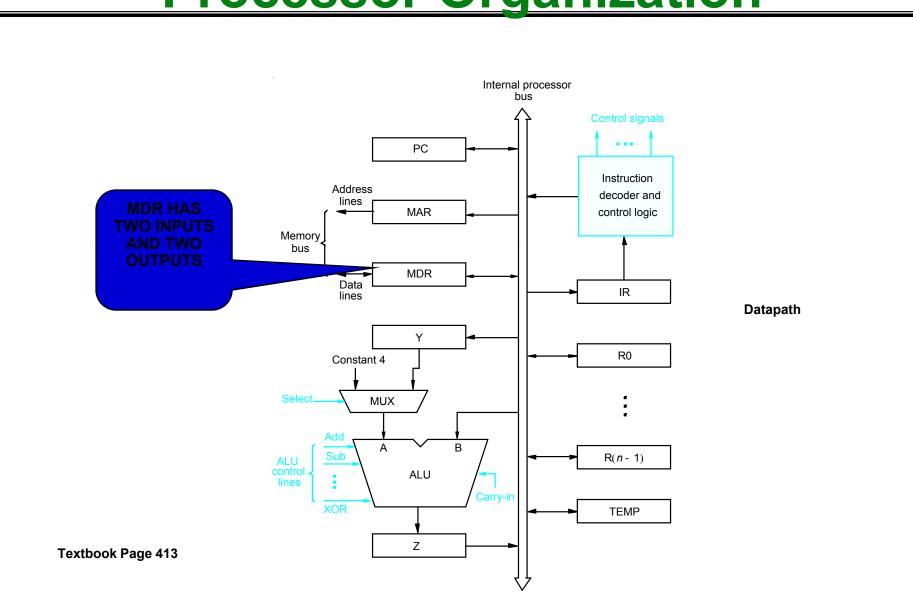

**Chap. 8: Central Processing Unit**

- General Register Organization

- Stack Organization,

Instruction Formats

- Addressing Modes

- Data Transfer and Manipulation

- Program Control

- Reduced Instruction Set Computer

**Computer Organization**

4

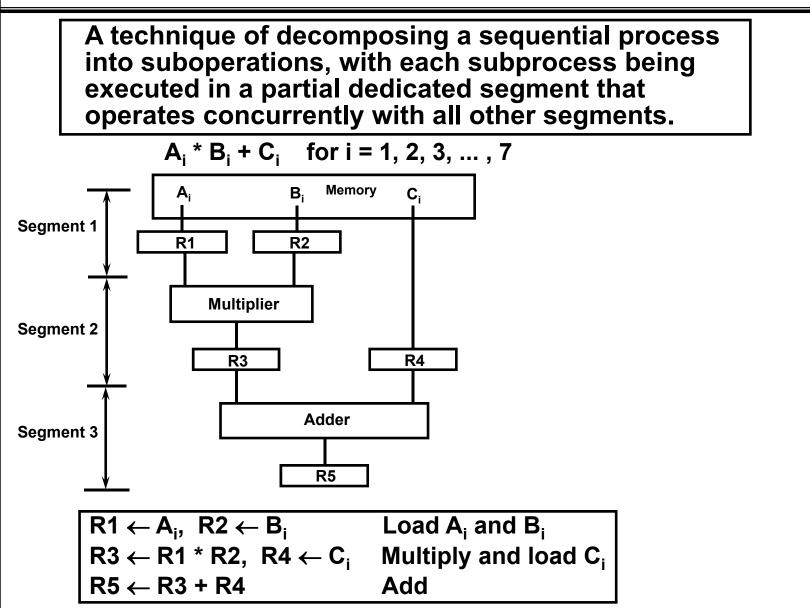

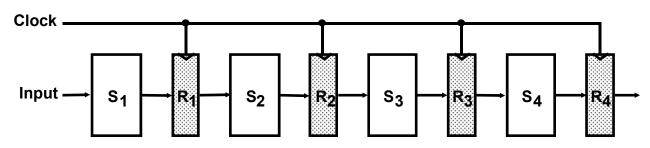

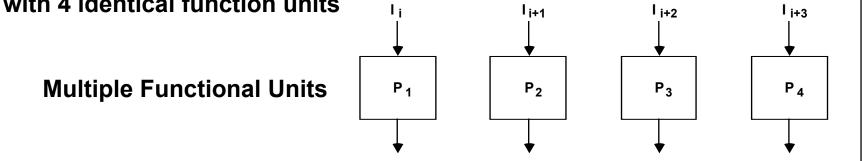

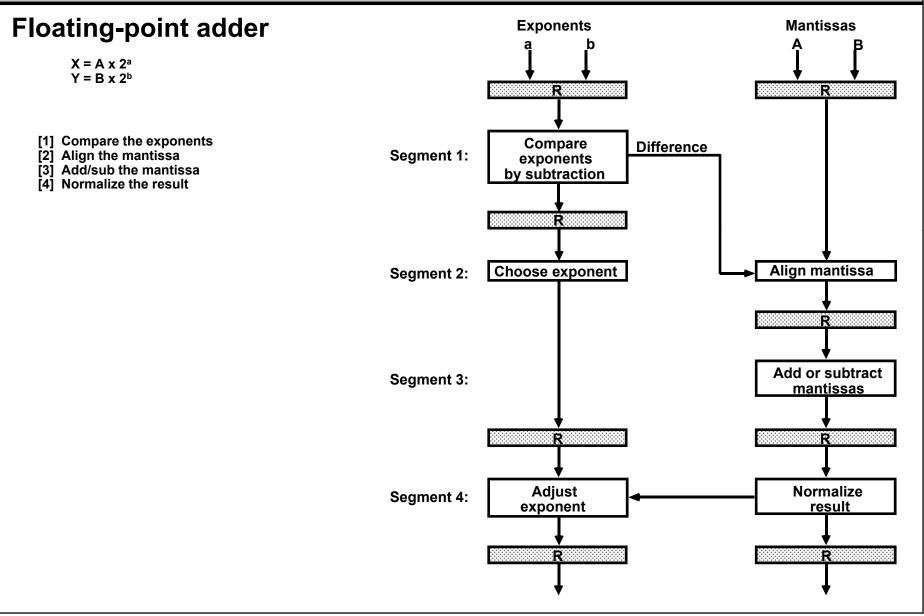

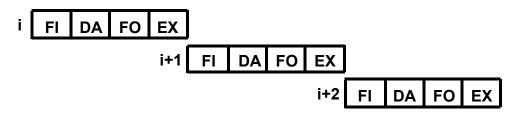

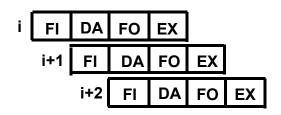

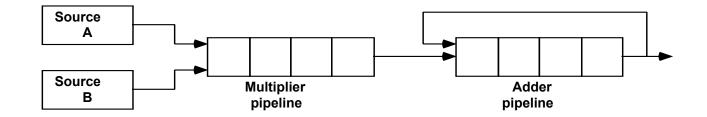

**Chap. 9: Pipeline and Vector Processing**

- Parallel Processing, Pipelining

- Arithmetic Pipeline, Instruction Pipeline

- RISC Pipeline,

Vector Processing

Chap. 10: Computer Arithmetic

- Arithmetic with Signed-2's Complement Numbers

- Multiplication and Division Algorithms

- Floating-Point Arithmetic Operations

- Decimal Arithmetic Unit

- Decimal Arithmetic Operations

#### Chap. 11: Input-Output Organization

- Peripheral Devices, Input-Output Interface

- Asynchronous Data Transfer, Modes of Transfer

- Priority Interrupt, Direct Memory Access

## SIMPLE DIGITAL SYSTEMS

- Combinational and sequential circuits (learned in Chapters 1 and 2) can be used to create simple digital systems.

- These are the low-level building blocks of a digital computer.

- Simple digital systems are frequently characterized in terms of

- the registers they contain, and

- the operations that they perform.

- Typically,

- What operations are performed on the data in the registers

- What information is passed between registers

## 8 **REGISTER TRANSFER AND MICROOPERATIONS** Register Transfer Language Register Transfer Bus and Memory Transfers Arithmetic Microoperations Logic Microoperations Shift Microoperations Arithmetic Logic Shift Unit

**Register Transfer & μ-operations**

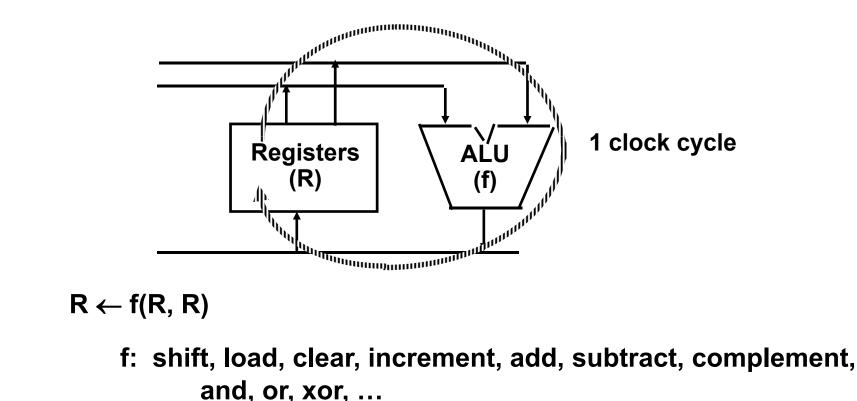

- The operations on the data in registers are called microoperations.

- The functions built into registers are examples of microoperations

- Shift

- Load

- Clear

- Increment

- ...

An elementary operation performed (during one clock pulse), on the information stored in one or more registers

**Computer Organization**

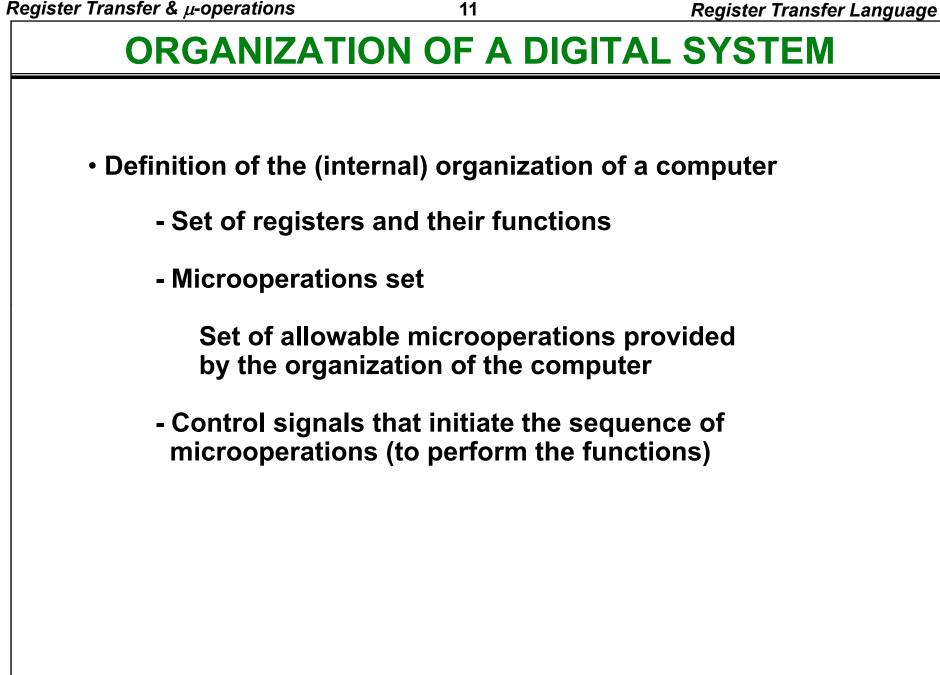

## **REGISTER TRANSFER LEVEL**

- Viewing a computer, or any digital system, in this way is called the register transfer level

- This is because we're focusing on

- The system's registers

- The data transformations in them, and

- The data transfers between them.

## **REGISTER TRANSFER LANGUAGE**

- Rather than specifying a digital system in words, a specific notation is used, *register transfer language*

- For any function of the computer, the register transfer language can be used to describe the (sequence of) microoperations

- Register transfer language

- A symbolic language

- A convenient tool for describing the internal organization of digital computers

- Can also be used to facilitate the design process of digital systems.

#### **DESIGNATION OF REGISTERS**

- Registers are designated by capital letters, sometimes followed by numbers (e.g., A, R13, IR)

- Often the names indicate function:

- MAR memory address register

- PC program counter

- IR instruction register

- Registers and their contents can be viewed and represented in various ways

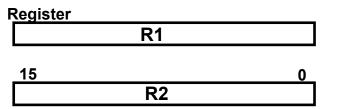

- A register can be viewed as a single entity:

MAR

- Registers may also be represented showing the bits of data they contain

#### **DESIGNATION OF REGISTERS**

- Designation of a register

- a register

- portion of a register

- a bit of a register

Common ways of drawing the block diagram of a register

Numbering of bits

| 7  | 65    | 4 | 3 | 2 | 1    | 0 |

|----|-------|---|---|---|------|---|

| 15 |       | 8 | 7 |   |      | 0 |

|    | PC(H) |   |   | P | C(L) |   |

Computer Organization

#### **REGISTER TRANSFER**

- Copying the contents of one register to another is a register transfer

- A register transfer is indicated as

#### **R2** ← **R1**

- In this case the contents of register R2 are copied (loaded) into register R1

- A simultaneous transfer of all bits from the source R1 to the destination register R2, during one clock pulse

- Note that this is a non-destructive; i.e. the contents of R1 are not altered by copying (loading) them to R2

#### **REGISTER TRANSFER**

- A register transfer such as

- R3 ← R5

Implies that the digital system has

- the data lines from the source register (R5) to the destination register (R3)

- Parallel load in the destination register (R3)

- Control lines to perform the action

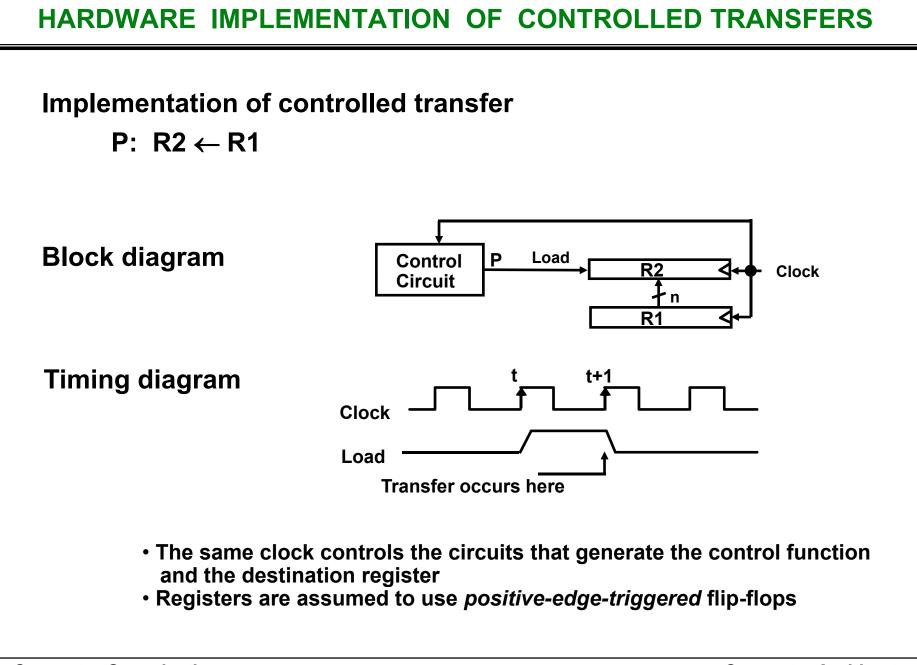

### **CONTROL FUNCTIONS**

- Often actions need to only occur if a certain condition is true

- This is similar to an "if" statement in a programming language

- In digital systems, this is often done via a control signal, called a control function

- If the signal is 1, the action takes place

- This is represented as:

P: R2 ← R1

Which means "if P = 1, then load the contents of register R1 into register R2", i.e., if (P = 1) then  $(R2 \leftarrow R1)$

19

**Computer Organization**

## **SIMULTANEOUS OPERATIONS**

• If two or more operations are to occur simultaneously, they are separated with commas

P:  $R3 \leftarrow R5$ , MAR  $\leftarrow IR$

Here, if the control function P = 1, load the contents of R5 into R3, and at the same time (clock), load the contents of register IR into register MAR

| <b>BASIC SYMBOLS FOR REGISTER TRANSFERS</b> |                                         |                                  |  |  |

|---------------------------------------------|-----------------------------------------|----------------------------------|--|--|

|                                             |                                         |                                  |  |  |

|                                             |                                         |                                  |  |  |

|                                             |                                         |                                  |  |  |

| O week a la                                 |                                         | <b>F</b>                         |  |  |

| Symbols                                     | Description                             | Examples                         |  |  |

| Capital letters<br>& numerals               | Denotes a register                      | MAR, R2                          |  |  |

| Parentheses ()                              | Denotes a part of a register            | R2(0-7), R2(L)                   |  |  |

| Arrow ←                                     | Denotes transfer of information         | R2 ← R1                          |  |  |

| Colon :                                     | Denotes termination of control function | P:                               |  |  |

| Comma ,                                     | Separates two micro-operations          | $A \leftarrow B, B \leftarrow A$ |  |  |

21

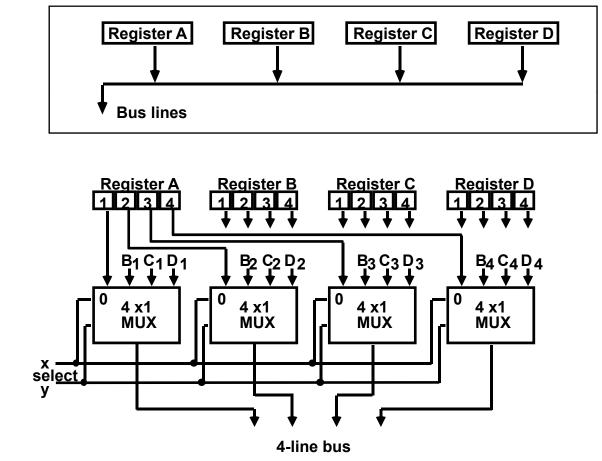

## **CONNECTING REGISTRS**

- In a digital system with many registers, it is impractical to have data and control lines to directly allow each register to be loaded with the contents of every possible other registers

- To completely connect n registers  $\rightarrow$  n(n-1) lines

- O(n<sup>2</sup>) cost

- This is not a realistic approach to use in a large digital system

- Instead, take a different approach

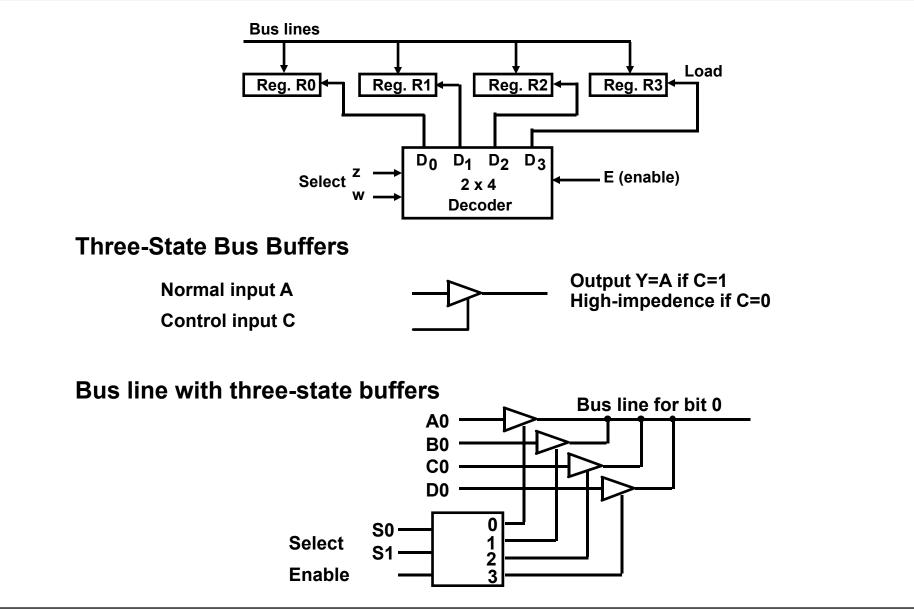

- Have one centralized set of circuits for data transfer the bus

- Have control circuits to select which register is the source, and which is the destination

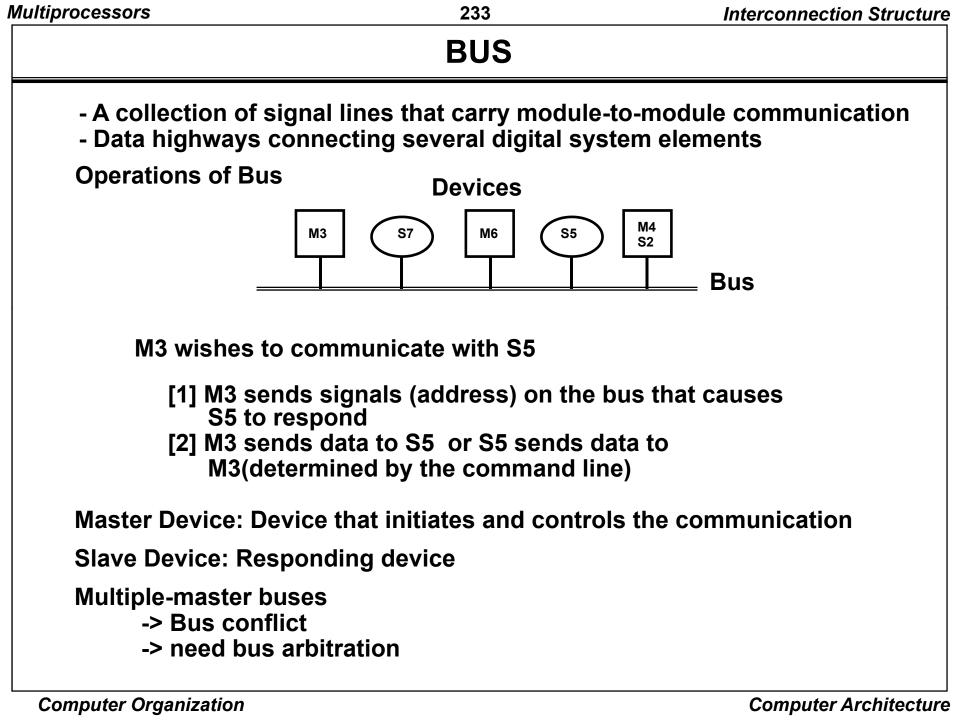

#### **BUS AND BUS TRANSFER**

Bus is a path(of a group of wires) over which information is transferred, from any of several sources to any of several destinations.

From a register to bus: BUS  $\leftarrow$  R

**Computer Organization**

#### TRANSFER FROM BUS TO A DESTINATION REGISTER

Computer Organization

#### **Computer Architecture**

24

#### **BUS TRANSFER IN RTL**

Depending on whether the bus is to be mentioned explicitly or not, register transfer can be indicated as either

R2 ← R1

or

$\text{BUS} \leftarrow \text{R1}, \text{R2} \leftarrow \text{BUS}$

In the former case the bus is implicit, but in the latter, it is explicitly indicated

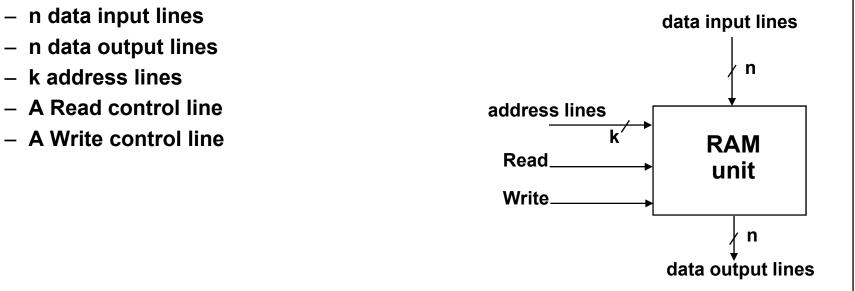

## **MEMORY (RAM)**

- Memory (RAM) can be thought as a sequential circuits containing some number of registers

- These registers hold the words of memory

- Each of the r registers is indicated by an *address*

- These addresses range from 0 to r-1

- Each register (word) can hold n bits of data

- Assume the RAM contains r = 2k words. It needs the following

#### MEMORY TRANSFER

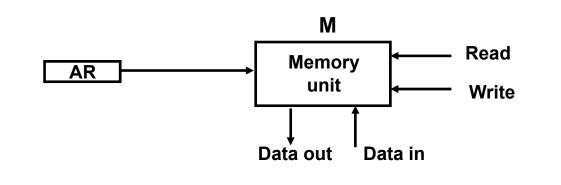

- Collectively, the memory is viewed at the register level as a device, M.

- Since it contains multiple locations, we must specify which address in memory we will be using

- This is done by indexing memory references

- Memory is usually accessed in computer systems by putting the desired address in a special register, the Memory Address Register (MAR, or AR)

- When memory is accessed, the contents of the MAR get sent to the memory unit's address lines

#### **MEMORY READ**

To read a value from a location in memory and load it into a register, the register transfer language notation looks like this:

#### $R1 \leftarrow M[MAR]$

- This causes the following to occur

- The contents of the MAR get sent to the memory address lines

- A Read (= 1) gets sent to the memory unit

- The contents of the specified address are put on the memory's output data lines

- These get sent over the bus to be loaded into register R1

#### **MEMORY WRITE**

To write a value from a register to a location in memory looks like this in register transfer language:

#### $M[MAR] \leftarrow R1$

- This causes the following to occur

- The contents of the MAR get sent to the memory address lines

- A Write (= 1) gets sent to the memory unit

- The values in register R1 get sent over the bus to the data input lines of the memory

- The values get loaded into the specified address in the memory

## **SUMMARY OF R. TRANSFER MICROOPERATIONS**

| A ← B                  | Transfer content of reg. B into reg. A                   |

|------------------------|----------------------------------------------------------|

| $AR \leftarrow DR(AD)$ | Transfer content of AD portion of reg. DR into reg. AR   |

| A ← constant           | Transfer a binary constant into reg. A                   |

| ABUS ← R1,             | Transfer content of R1 into bus A and, at the same time, |

| R2 ← ABUS              | transfer content of bus A into R2                        |

| AR                     | Address register                                         |

| DR                     | Data register                                            |

| M[R]                   | Memory word specified by reg. R                          |

| Μ                      | Equivalent to M[AR]                                      |

| $DR \leftarrow M$      | Memory read operation: transfers content of              |

|                        | memory word specified by AR into DR                      |

| M← DR                  | Memory write operation: transfers content of             |

|                        | DR into memory word specified by AR                      |

30

#### MICROOPERATIONS

Computer system microoperations are of four types:

- Register transfer microoperations

- Arithmetic microoperations

- Logic microoperations

- Shift microoperations

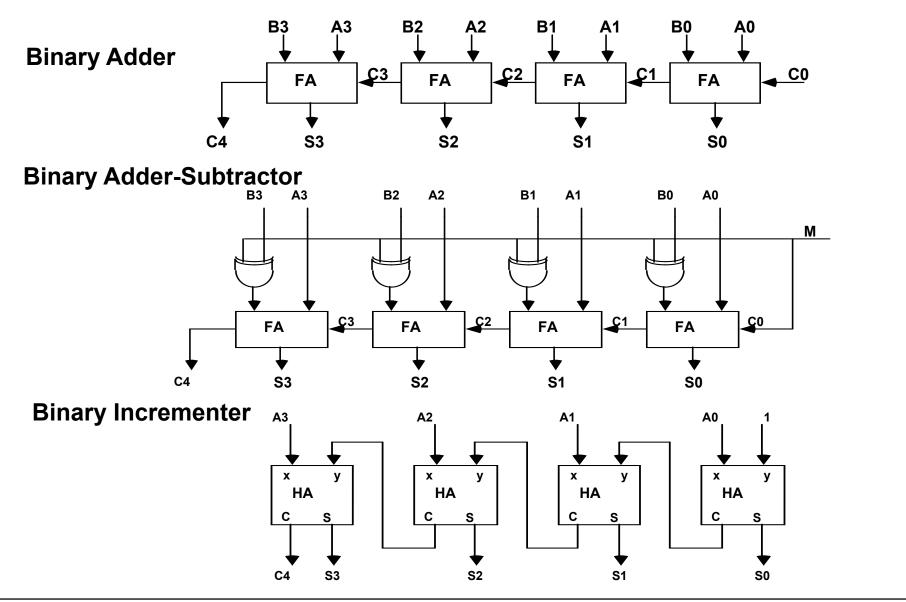

## **ARITHMETIC MICROOPERATIONS**

- The basic arithmetic microoperations are

- Addition

- Subtraction

- Increment

- Decrement

- The additional arithmetic microoperations are

- Add with carry

- Subtract with borrow

- Transfer/Load

- etc. ...

#### **Summary of Typical Arithmetic Micro-Operations**

| R3 ← R1 + R2     | Contents of R1 plus R2 transferred to R3   |

|------------------|--------------------------------------------|

| R3 ← R1 - R2     | Contents of R1 minus R2 transferred to R3  |

| R2 ← R2'         | Complement the contents of R2              |

| R2 ← R2'+ 1      | 2's complement the contents of R2 (negate) |

| R3 ← R1 + R2'+ 1 | subtraction                                |

| R1 ← R1 + 1      | Increment                                  |

| R1 ← R1 - 1      | Decrement                                  |

## **BINARY ADDER / SUBTRACTOR / INCREMENTER**

#### Computer Organization

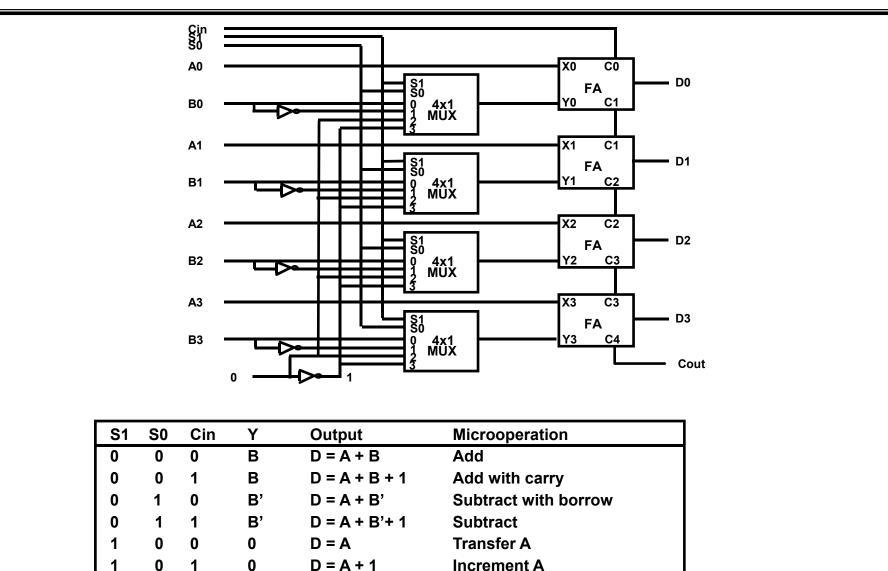

#### **ARITHMETIC CIRCUIT**

**Decrement A**

**Transfer A**

Computer Organization

1

0

1

D = A - 1

$\mathbf{D} = \mathbf{A}$

**Computer Architecture**

34

#### LOGIC MICROOPERATIONS

- Specify binary operations on the strings of bits in registers

- Logic microoperations are bit-wise operations, i.e., they work on the individual bits of data

- useful for bit manipulations on binary data

- useful for making logical decisions based on the bit value

- There are, in principle, 16 different logic functions that can be defined over two binary input variables

| Α | В | F <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> F <sub>13</sub> F <sub>14</sub> F <sub>15</sub> |

|---|---|----------------|----------------|----------------------------------------------------------------|

| 0 | 0 | 0              | 0              | 0 1 1 1                                                        |

| 0 | 1 | 0              | 0              | 0 1 1 1<br>0 1 1 1                                             |

| 1 | 0 | 0              | 0              | 1 0 1 1                                                        |

| 1 | 1 | 0              | 1              | 0 1 0 1                                                        |

- However, most systems only implement four of these

- AND ( $\land$ ), OR ( $\lor$ ), XOR (⊕), Complement/NOT

- The others can be created from combination of these

#### LIST OF LOGIC MICROOPERATIONS

- List of Logic Microoperations

- 16 different logic operations with 2 binary vars.

- n binary vars  $\rightarrow$  2<sup>2<sup>n</sup></sup> functions

- Truth tables for 16 functions of 2 variables and the corresponding 16 logic micro-operations

| 0 0 1 1<br>0 1 0 1 | Boolean<br>Function | Micro-<br>Operations                | Name           |

|--------------------|---------------------|-------------------------------------|----------------|

| 0000               | F0 = 0              | F ← 0                               | Clear          |

| 0001               | F1 = xy             | F←A∧B                               | AND            |

| 0010               | F2 = xy'            | F ← A ∧ B'                          |                |

| 0011               | F3 = x              | F←A                                 | Transfer A     |

| 0100               | F4 = x'y            | F ← A'∧ B                           |                |

| 0101               | F5 = y              | F ← B                               | Transfer B     |

| 0110               | F6 = x ⊕ y          | F   ←   A   ⊕   B                   | Exclusive-OR   |

| 0111               | F7 = x + y          | $F \leftarrow A \lor B$             | OR             |

| 1000               | F8 = (x + y)'       | F ← (A ∨ B)'                        | NOR            |

| 1001               | F9 = (x ⊕ y)'       | <b>F</b> ← ( <b>A</b> ⊕ <b>B</b> )' | Exclusive-NOR  |

| 1010               | F10 = y'            | F ← B'                              | Complement B   |

| 1011               | F11 = x + y'        | $F \leftarrow A \lor B$             |                |

| 1100               | F12 = x'            | F ← A'                              | Complement A   |

| 1101               | F13 = x' + y        | F   ←   A'∨ B                       | -              |

| 1110               | F14 = (xy)          | F ← (A ∧ B)'                        | NAND           |

| 1111               | F15 = 1             | F ← all 1's                         | Set to all 1's |

Computer Organization

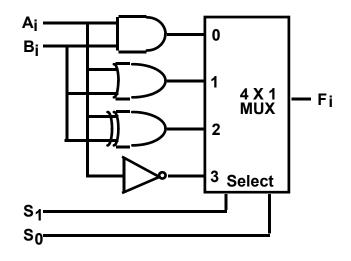

### HARDWARE IMPLEMENTATION OF LOGIC MICROOPERATIONS

#### **Function table**

| <b>S</b> <sub>1</sub> | S <sub>0</sub> | Output           | μ-operation |

|-----------------------|----------------|------------------|-------------|

| 0                     | 0              | $F = A \land B$  | AND         |

| 0                     | 1              | $F = A \lor B$   | OR          |

| 1                     | 0              | $F = A \oplus B$ | XOR         |

| 1                     | 1              | F = A'           | Complement  |

**Computer Organization**

# **APPLICATIONS OF LOGIC MICROOPERATIONS**

- Logic microoperations can be used to manipulate individual bits or a portions of a word in a register

- Consider the data in a register A. In another register, B, is bit data that will be used to modify the contents of A

| <ul> <li>Selective-set</li> </ul>        | $A \leftarrow A + B$                                 |

|------------------------------------------|------------------------------------------------------|

| <ul> <li>Selective-complement</li> </ul> | $\mathbf{A} \leftarrow \mathbf{A} \oplus \mathbf{B}$ |

| <ul> <li>Selective-clear</li> </ul>      | A ← A • B'                                           |

| <ul> <li>Mask (Delete)</li> </ul>        | $A \leftarrow A \bullet B$                           |

| – Clear                                  | $\mathbf{A} \leftarrow \mathbf{A} \oplus \mathbf{B}$ |

| – Insert                                 | $A \leftarrow (A \bullet B) + C$                     |

| <ul> <li>Compare</li> </ul>              | $A \leftarrow A \oplus B$                            |

- ...

# **SELECTIVE SET**

In a selective set operation, the bit pattern in B is used to set certain bits in A

| 1100 | A <sub>t</sub>   |             |

|------|------------------|-------------|

| 1010 | В                |             |

| 1110 | A <sub>t+1</sub> | (A ← A + B) |

• If a bit in B is set to 1, that same position in A gets set to 1, otherwise that bit in A keeps its previous value

# SELECTIVE COMPLEMENT

In a selective complement operation, the bit pattern in B is used to *complement* certain bits in A

| 1100 | A <sub>t</sub>   |             |

|------|------------------|-------------|

| 1010 | В                |             |

| 0110 | A <sub>t+1</sub> | (A ← A ⊕ B) |

If a bit in B is set to 1, that same position in A gets complemented from its original value, otherwise it is unchanged

# **SELECTIVE CLEAR**

• In a selective clear operation, the bit pattern in B is used to *clear* certain bits in A

| 1100 | A <sub>t</sub>   |              |

|------|------------------|--------------|

| 1010 | В                |              |

| 0100 | A <sub>t+1</sub> | (A ← A · B') |

If a bit in B is set to 1, that same position in A gets set to 0, otherwise it is unchanged

# **MASK OPERATION**

In a mask operation, the bit pattern in B is used to *clear* certain bits in A

| 1100 | <b>A</b> t       |                            |

|------|------------------|----------------------------|

| 1010 | В                |                            |

| 1000 | A <sub>t+1</sub> | $(A \leftarrow A \cdot B)$ |

If a bit in B is set to 0, that same position in A gets set to 0, otherwise it is unchanged

# **CLEAR OPERATION**

In a clear operation, if the bits in the same position in A and B are the same, they are cleared in A, otherwise they are set in A

| 1100 | <b>A</b> t       |             |

|------|------------------|-------------|

| 1010 | В                |             |

| 0110 | A <sub>t+1</sub> | (A ← A ⊕ B) |

**Register Transfer & μ-operations**

## **INSERT OPERATION**

- An insert operation is used to introduce a specific bit pattern into A register, leaving the other bit positions unchanged

- This is done as

- A mask operation to clear the desired bit positions, followed by

- An OR operation to introduce the new bits into the desired positions

- Example

- » Suppose you wanted to introduce 1010 into the low order four bits of A: 1101 1000 1011 0001 A (Original) 1101 1000 1011 1010 A (Desired)

| <b>»</b> | 1101 | 1000 | 1011 | 0001 | A (Original)     |

|----------|------|------|------|------|------------------|

|          | 1111 | 1111 | 1111 | 0000 | Mask             |

|          | 1101 | 1000 | 1011 | 0000 | A (Intermediate) |

|          | 0000 | 0000 | 0000 | 1010 | Added bits       |

|          | 1101 | 1000 | 1011 | 1010 | A (Desired)      |

**Computer Organization**

44

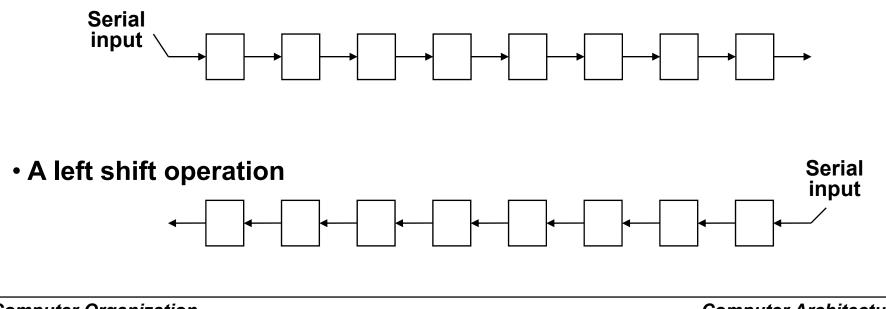

## SHIFT MICROOPERATIONS

- There are three types of shifts

- Logical shift

- Circular shift

- Arithmetic shift

- What differentiates them is the information that goes into the serial input

- A right shift operation

**Computer Organization**

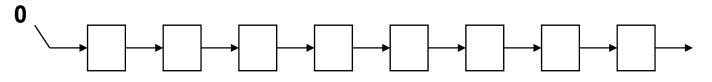

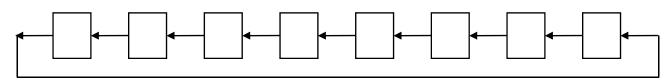

### LOGICAL SHIFT

- In a logical shift the serial input to the shift is a 0.

- A right logical shift operation:

• A left logical shift operation:

- shl for a logical shift left

- *shr* for a logical shift right

- Examples:

- » R2 ← *shr* R2

- » R3 ← *shl* R3

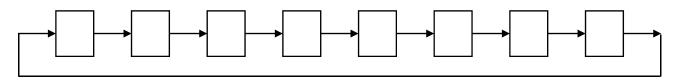

### **CIRCULAR SHIFT**

- In a circular shift the serial input is the bit that is shifted out of the other end of the register.

- A right circular shift operation:

• A left circular shift operation:

- In a RTL, the following notation is used

- cil for a circular shift left

- cir for a circular shift right

- Examples:

- » R2 *← cir* R2

- » R3  $\leftarrow$  cil R3

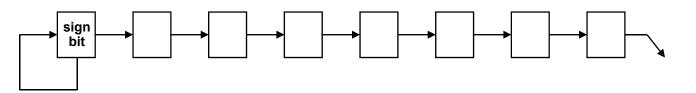

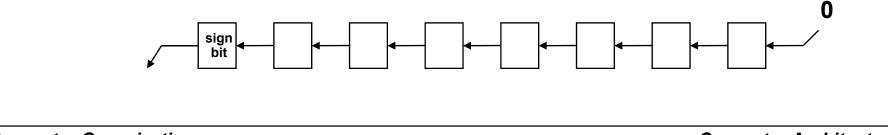

### **ARITHMETIC SHIFT**

- An arithmetic shift is meant for signed binary numbers (integer)

- An arithmetic left shift multiplies a signed number by two

- An arithmetic right shift divides a signed number by two

- The main distinction of an arithmetic shift is that it must keep the sign of the number the same as it performs the multiplication or division

- A right arithmetic shift operation:

• A left arithmetic shift operation:

**Computer Organization**

**Computer Architecture**

48

### **ARITHMETIC SHIFT**

An left arithmetic shift operation must be checked for the overflow

- In a RTL, the following notation is used

- ashl for an arithmetic shift left

- *ashr* for an arithmetic shift right

- Examples:

- » R2 ← ashr R2

- » R3 ← ashl R3

**Computer Organization**

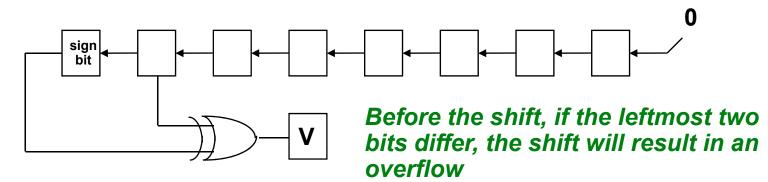

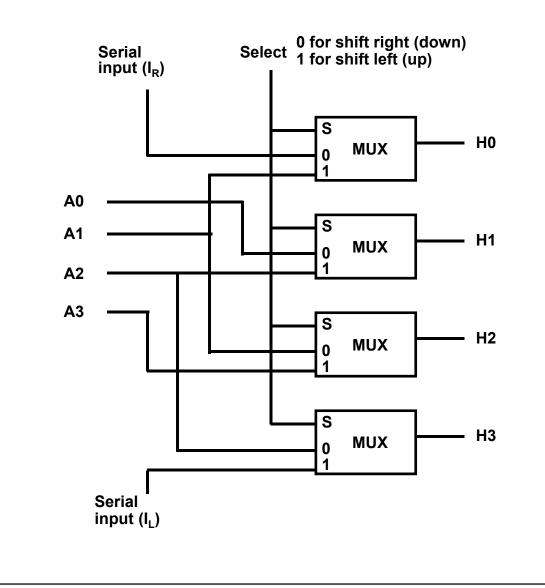

#### HARDWARE IMPLEMENTATION OF SHIFT MICROOPERATIONS

**Computer Organization**

**Computer Architecture**

50

#### 51 **ARITHMETIC LOGIC SHIFT UNIT** S3 S2 S1 Ċi S0 Arithmetic Di Circuit Select 0 4 x 1 1 MUX ۶F C<sub>i+1</sub> 2 3 Εi Logic Circuit B<sub>i</sub>-Ai shr $A_{i-1}$ shl A<sub>i+1</sub> S3 S2 S1 S0 Cin Operation Function

| 0 | 0 | 0 | 0 | 0 | F = A         | Transfer A           |  |

|---|---|---|---|---|---------------|----------------------|--|

| 0 | 0 | 0 | 0 | 1 | F = A + 1     | Increment A          |  |

| 0 | 0 | 0 | 1 | 0 | F = A + B     | Addition             |  |

| 0 | 0 | 0 | 1 | 1 | F = A + B + 1 | Add with carry       |  |

| 0 | 0 | 1 | 0 | 0 | F = A + B'    | Subtract with borrow |  |

| 0 | 0 | 1 | 0 | 1 | F = A + B'+ 1 | Subtraction          |  |

| 0 | 0 | 1 | 1 | 0 | F = A - 1     | Decrement A          |  |

| 0 | 0 | 1 | 1 | 1 | F = A         | TransferA            |  |

| 0 | 1 | 0 | 0 | X | F = A ∧ B     | AND                  |  |

| 0 | 1 | 0 | 1 | X | F = A ∨ B     | OR                   |  |

| 0 | 1 | 1 | 0 | X | F = A ⊕ B     | XOR                  |  |

| 0 | 1 | 1 | 1 | X | F = A'        | Complement A         |  |

| 1 | 0 | Χ | Х | X | F = shr A     | Shift right A into F |  |

| 1 | 1 | Χ | Χ | X | F = shl A     | Shift left A into F  |  |

| l |   |   |   |   |               | 1                    |  |

Computer Organization

# **BASIC COMPUTER ORGANIZATION AND DESIGN**

- Instruction Codes

- Computer Registers

- Computer Instructions

- Timing and Control

- Instruction Cycle

- Memory Reference Instructions

- Input-Output and Interrupt

- Complete Computer Description

- Design of Basic Computer

- Design of Accumulator Logic

# INTRODUCTION

- Every different processor type has its own design (different registers, buses, microoperations, machine instructions, etc)

- Modern processor is a very complex device

- It contains

- Many registers

- Multiple arithmetic units, for both integer and floating point calculations

- The ability to pipeline several consecutive instructions to speed execution

- Etc.

- However, to understand how processors work, we will start with a simplified processor model

- This is similar to what real processors were like ~25 years ago

- M. Morris Mano introduces a simple processor model he calls the *Basic Computer*

- We will use this to introduce processor organization and the relationship of the RTL model to the higher level computer processor

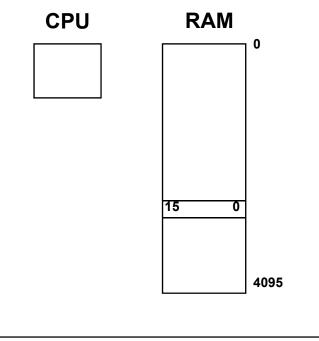

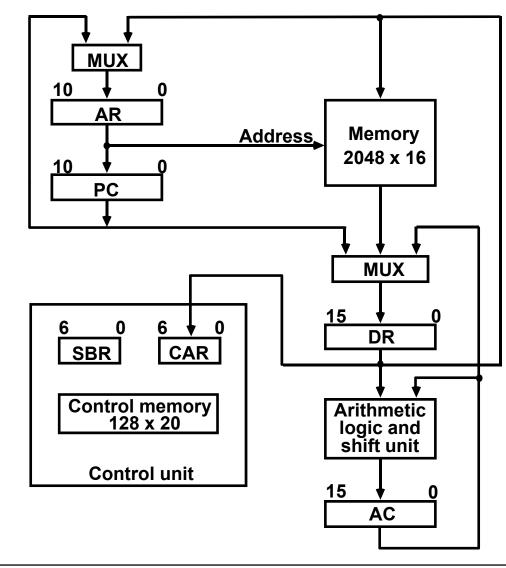

# THE BASIC COMPUTER

- The Basic Computer has two components, a processor and memory

- The memory has 4096 words in it

- 4096 =  $2^{12}$ , so it takes 12 bits to select a word in memory

- Each word is 16 bits long

### INSTRUCTIONS

- Program

- A sequence of (machine) instructions

- (Machine) Instruction

- A group of bits that tell the computer to *perform a specific operation* (a sequence of micro-operation)

- The instructions of a program, along with any needed data are stored in memory

- The CPU reads the next instruction from memory

- It is placed in an Instruction Register (IR)

- Control circuitry in control unit then translates the instruction into the sequence of microoperations necessary to implement it

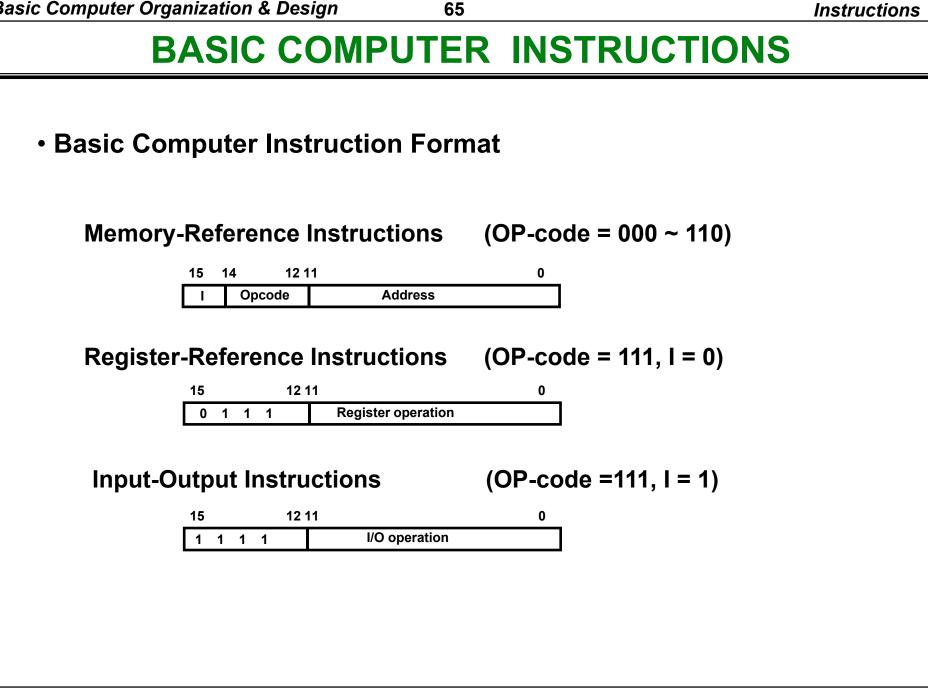

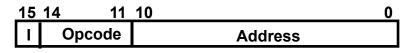

### **INSTRUCTION FORMAT**

- A computer instruction is often divided into two parts

- An opcode (Operation Code) that specifies the operation for that instruction

- An address that specifies the registers and/or locations in memory to use for that operation

- In the Basic Computer, since the memory contains 4096 (= 2<sup>12</sup>) words, we needs 12 bit to specify which memory address this instruction will use

- In the Basic Computer, bit 15 of the instruction specifies the *addressing mode* (0: direct addressing, 1: indirect addressing)

- Since the memory words, and hence the instructions, are 16 bits long, that leaves 3 bits for the instruction's opcode

| Instruction Format  |         |   |

|---------------------|---------|---|

| 15 14 12 1          | 11      | 0 |

| <sup>I</sup> Opcode | Address |   |

| R                   |         |   |

| Addressing<br>mode  |         |   |

**Computer Organization**

**Computer Architecture**

56

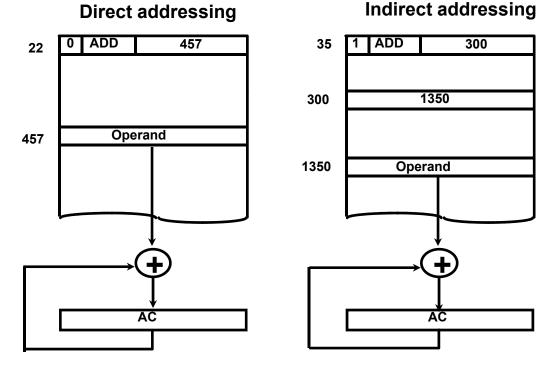

# **ADDRESSING MODES**

- The address field of an instruction can represent either

- Direct address: the address in memory of the data to use (the address of the operand), or

- Indirect address: the address in memory of the address in memory of the data to use

### • Effective Address (EA)

The address, that can be directly used without modification to access an operand for a computation-type instruction, or as the target address for a branch-type instruction

Computer Organization

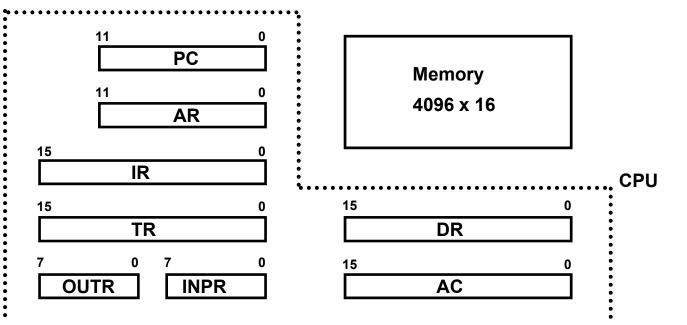

### **PROCESSOR REGISTERS**

- A processor has many registers to hold instructions, addresses, data, etc

- The processor has a register, the *Program Counter* (PC) that holds the memory address of the next instruction to get

- Since the memory in the Basic Computer only has 4096 locations, the PC only needs 12 bits

- In a direct or indirect addressing, the processor needs to keep track of what locations in memory it is addressing: The Address Register (AR) is used for this

- The AR is a 12 bit register in the Basic Computer

- When an operand is found, using either direct or indirect addressing, it is placed in the *Data Register* (DR). The processor then uses this value as data for its operation

- The Basic Computer has a single general purpose register the Accumulator (AC)

# **PROCESSOR REGISTERS**

- The significance of a general purpose register is that it can be referred to in instructions

- e.g. load AC with the contents of a specific memory location; store the contents of AC into a specified memory location

- Often a processor will need a scratch register to store intermediate results or other temporary data; in the Basic Computer this is the *Temporary Register* (TR)

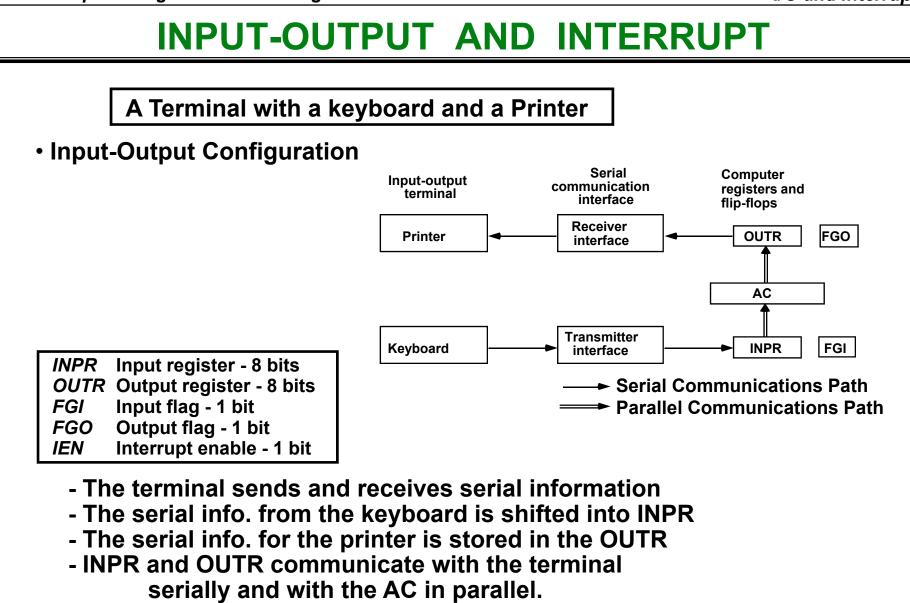

- The Basic Computer uses a very simple model of input/output (I/O) operations

- Input devices are considered to send 8 bits of character data to the processor

- The processor can send 8 bits of character data to output devices

- The Input Register (INPR) holds an 8 bit character gotten from an input device

- The *Output Register* (OUTR) holds an 8 bit character to be send to an output device

## **BASIC COMPUTER REGISTERS**

#### **List of BC Registers**

| DR   | 16 | Data Register        | Holds memory operand         |

|------|----|----------------------|------------------------------|

| AR   | 12 | Address Register     | Holds address for memory     |

| AC   | 16 | Accumulator          | Processor register           |

| IR   | 16 | Instruction Register | Holds instruction code       |

| PC   | 12 | Program Counter      | Holds address of instruction |

| TR   | 16 | Temporary Register   | Holds temporary data         |

| INPR | 8  | Input Register       | Holds input character        |

| OUTR | 8  | Output Register      | Holds output character       |

**Computer Organization**

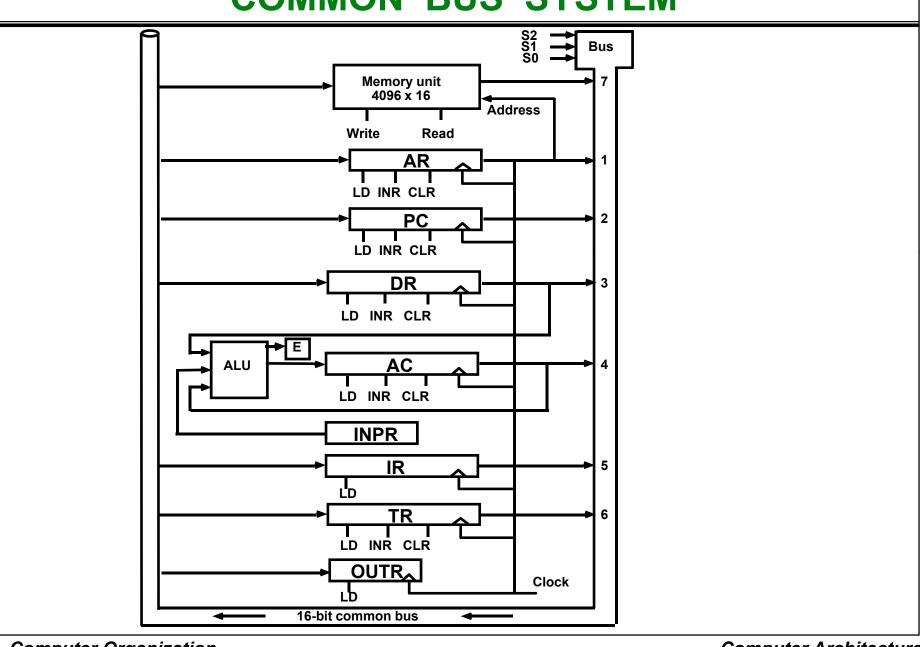

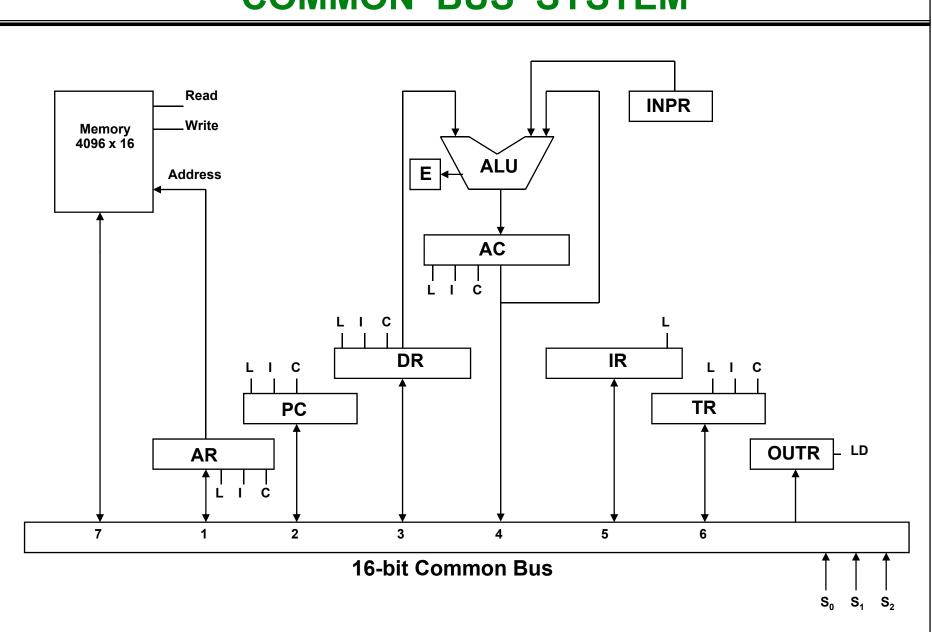

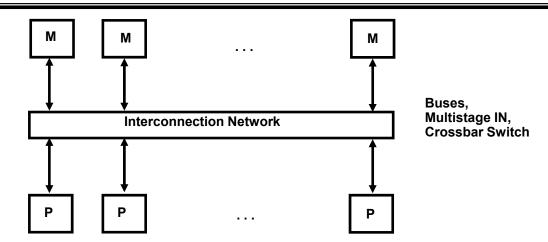

## COMMON BUS SYSTEM

- The registers in the Basic Computer are connected using a bus

- This gives a savings in circuitry over complete connections between registers

**Basic Computer Organization & Design**

### **COMMON BUS SYSTEM**

**Computer Organization**

**Basic Computer Organization & Design**

#### Registers

### **COMMON BUS SYSTEM**

Computer Organization

### COMMON BUS SYSTEM

Three control lines, S<sub>2</sub>, S<sub>1</sub>, and S<sub>0</sub> control which register the bus selects as its input

| <b>S</b> <sub>2</sub> <b>S</b> <sub>1</sub> | S <sub>0</sub> | Register |

|---------------------------------------------|----------------|----------|

| 0 0                                         | 0              | X        |

| 0 0                                         | 1              | AR       |

| 0 1                                         | 0              | РС       |

| 0 1                                         | 1              | DR       |

| 1 0                                         | 0              | AC       |

| 1 0                                         | 1              | IR       |

| 1 1                                         | 0              | TR       |

| 1 1                                         | 1              | Memory   |

- Either one of the registers will have its load signal activated, or the memory will have its read signal activated

- Will determine where the data from the bus gets loaded

- The 12-bit registers, AR and PC, have 0's loaded onto the bus in the high order 4 bit positions

- When the 8-bit register OUTR is loaded from the bus, the data comes from the low order 8 bits on the bus

### **BASIC COMPUTER INSTRUCTIONS**

| Hex Code |       |              |                                    |  |

|----------|-------|--------------|------------------------------------|--|

| Symbol   | 1 = 0 | <i>l</i> = 1 | Description                        |  |

| AND      | 0xxx  | 8xxx         | AND memory word to AC              |  |

| ADD      | 1xxx  | 9xxx         | Add memory word to AC              |  |

| LDA      | 2xxx  | Axxx         | Load AC from memory                |  |

| STA      | 3xxx  | Bxxx         | Store content of AC into memory    |  |

| BUN      | 4xxx  | Cxxx         | Branch unconditionally             |  |

| BSA      | 5xxx  | Dxxx         | Branch and save return address     |  |

| ISZ      | 6xxx  | Exxx         | Increment and skip if zero         |  |

| CLA      | 7800  |              | Clear AC                           |  |

| CLE      | 7400  |              | Clear E                            |  |

| СМА      | 7200  |              | Complement AC                      |  |

| CME      | 7100  |              | Complement E                       |  |

| CIR      | 7080  |              | Circulate right AC and E           |  |

| CIL      | 7040  |              | Circulate left AC and E            |  |

| INC      | 7020  |              | Increment AC                       |  |

| SPA      | 7010  |              | Skip next instr. if AC is positive |  |

| SNA      | 7008  |              | Skip next instr. if AC is negative |  |

| SZA      | 7004  |              | Skip next instr. if AC is zero     |  |

| SZE      | 7002  |              | Skip next instr. if E is zero      |  |

| HLT      | 7001  |              | Halt computer                      |  |

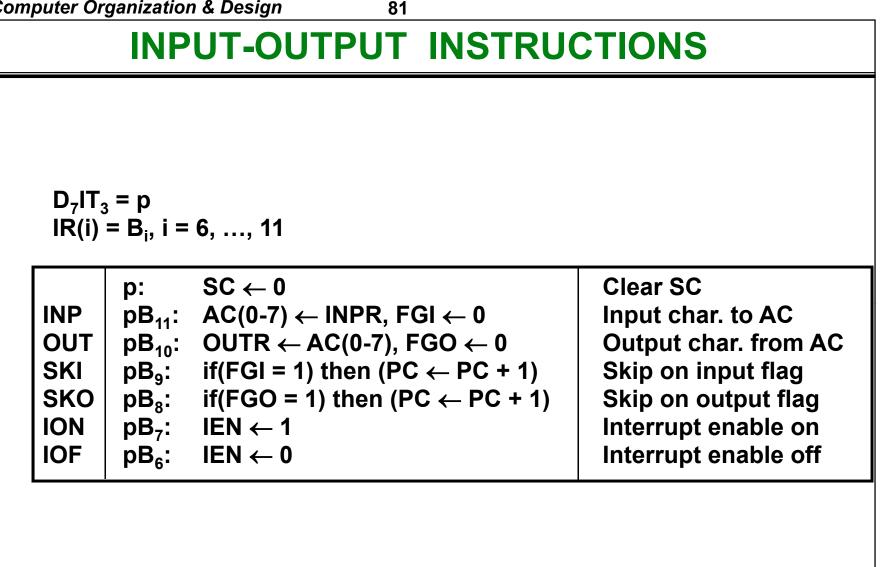

| INP      | F800  |              | Input character to AC              |  |

| OUT      | F400  |              | Output character from AC           |  |

| SKI      | F2    | 00           | Skip on input flag                 |  |

| SKO      | F100  |              | Skip on output flag                |  |

| ION      | F080  |              | Interrupt on                       |  |

| IOF      | F0    | 40           | Interrupt off                      |  |

**Computer Organization**

# **INSTRUCTION SET COMPLETENESS**

A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is known to be computable.

- Instruction Types

- **Functional Instructions**

- Arithmetic, logic, and shift instructions

- ADD, CMA, INC, CIR, CIL, AND, CLA

- **Transfer Instructions**

- Data transfers between the main memory and the processor registers

- LDA, STA

- **Control Instructions**

- Program sequencing and control

- BUN, BSA, ISZ

- **Input/Output Instructions**

- Input and output

- INP, OUT

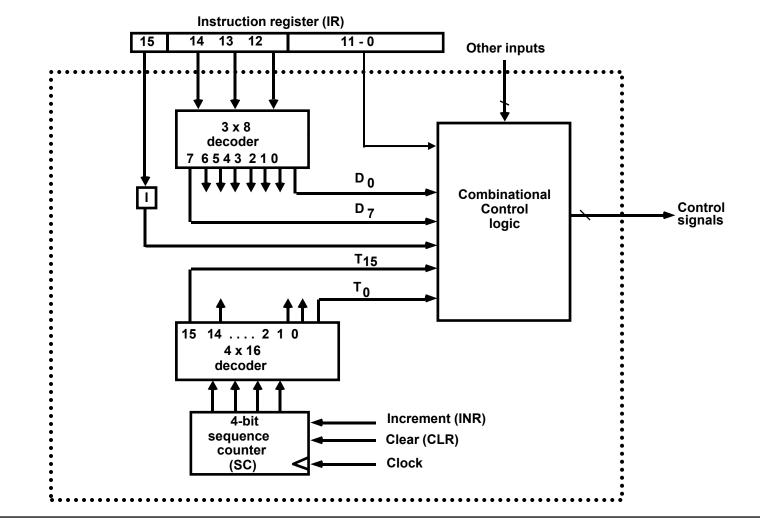

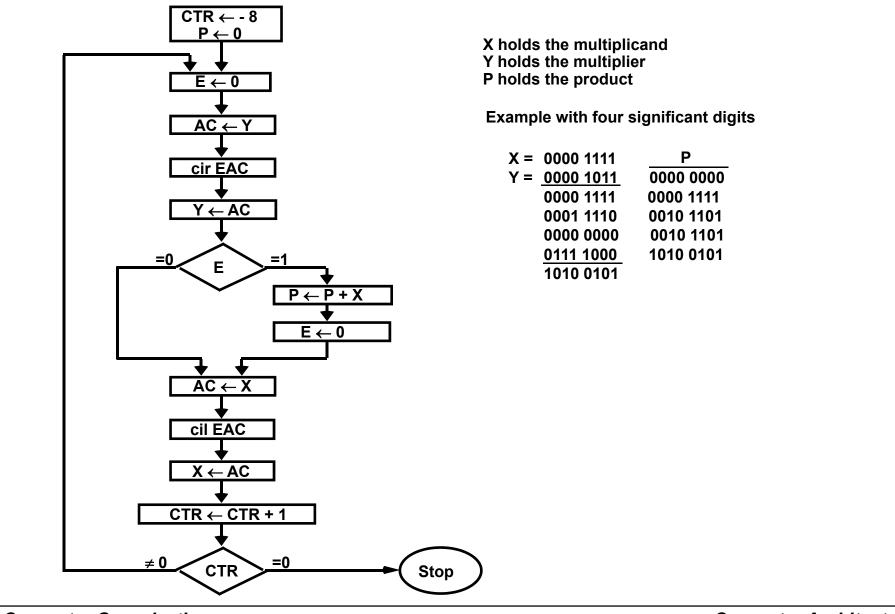

### **CONTROL UNIT**

- Control unit (CU) of a processor translates from machine instructions to the control signals for the microoperations that implement them

- Control units are implemented in one of two ways

- Hardwired Control

- CU is made up of sequential and combinational circuits to generate the control signals

- Microprogrammed Control

- A control memory on the processor contains microprograms that activate the necessary control signals

- We will consider a hardwired implementation of the control unit for the Basic Computer

### TIMING AND CONTROL

### **Control unit of Basic Computer**

Computer Organization

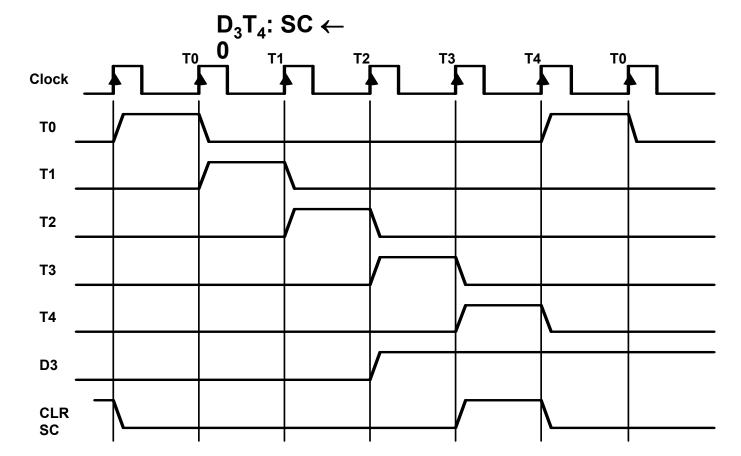

### TIMING SIGNALS

- Generated by 4-bit sequence counter and 4×16 decoder

- The SC can be incremented or cleared.

- Example:  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ,  $T_0$ ,  $T_1$ , . . . Assume: At time  $T_4$ , SC is cleared to 0 if decoder output D3 is active.

**Computer Organization**

Basic Computer Organization & Design

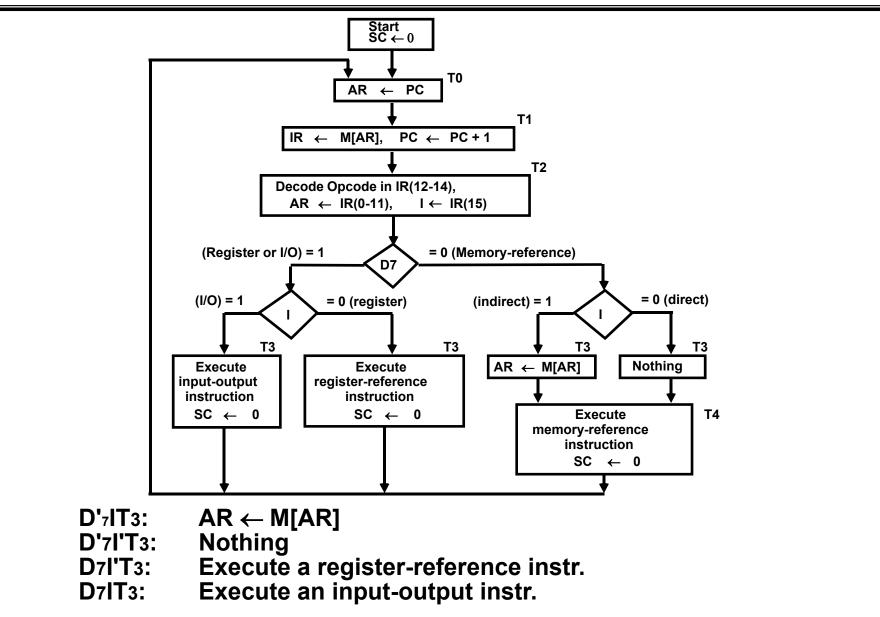

### **INSTRUCTION CYCLE**

- In Basic Computer, a machine instruction is executed in the following cycle:

- 1. Fetch an instruction from memory

- 2. Decode the instruction

- 3. Read the effective address from memory if the instruction has an indirect address

- 4. Execute the instruction

- After an instruction is executed, the cycle starts again at step 1, for the next instruction

- Note: Every different processor has its own (different) instruction cycle

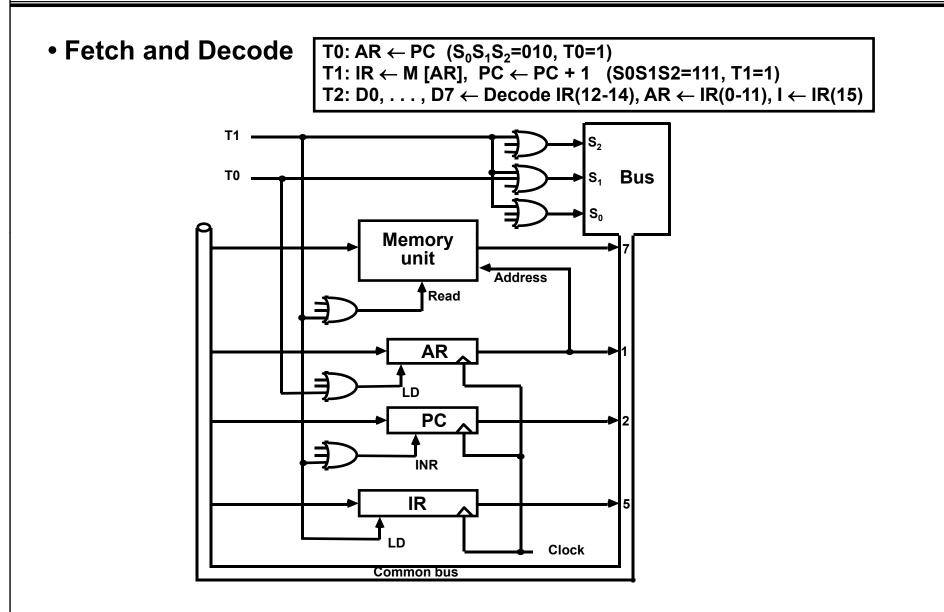

### **FETCH and DECODE**

72

**Computer Organization**

### DETERMINE THE TYPE OF INSTRUCTION

**Computer Organization**

# **REGISTER REFERENCE INSTRUCTIONS**

**Register Reference Instructions are identified when**

- $D_7 = 1$ , I = 0

- Register Ref. Instr. is specified in  $b_0 \sim b_{11}$  of IR

- Execution starts with timing signal  $T_3$

r = D<sub>7</sub> I'T<sub>3</sub> => Register Reference Instruction B<sub>i</sub> = IR(i) , i=0,1,2,...,11

|     | r:                 | SC ← 0                                                          |

|-----|--------------------|-----------------------------------------------------------------|

| CLA | rB₁₁:              | $AC \leftarrow 0$                                               |

| CLE | rB <sub>10</sub> : | E ← 0                                                           |

| CMA | rB <sub>9</sub> :  | $AC \leftarrow AC'$                                             |

| CME | rB <sub>8</sub> :  | E ← E'                                                          |

| CIR | rB <sub>7</sub> :  | $AC \leftarrow shr AC, AC(15) \leftarrow E, E \leftarrow AC(0)$ |

| CIL | rB <sub>6</sub> :  | $AC \leftarrow shl AC, AC(0) \leftarrow E, E \leftarrow AC(15)$ |

| INC | rB <sub>5</sub> :  | $AC \leftarrow AC + 1$                                          |

| SPA | rB₄:               | if (AC(15) = 0) then (PC ← PC+1)                                |

| SNA | $rB_3$ :           | if $(AC(15) = 1)$ then $(PC \leftarrow PC+1)$                   |

| SZA | $rB_2$ :           | if (AC = 0) then (PC ← PC+1)                                    |

| SZE | rB₁ً:              | if $(E = 0)$ then $(PC \leftarrow PC+1)$                        |

| HLT | rB <sub>0</sub> :  | $S \leftarrow 0$ (S is a start-stop flip-flop)                  |

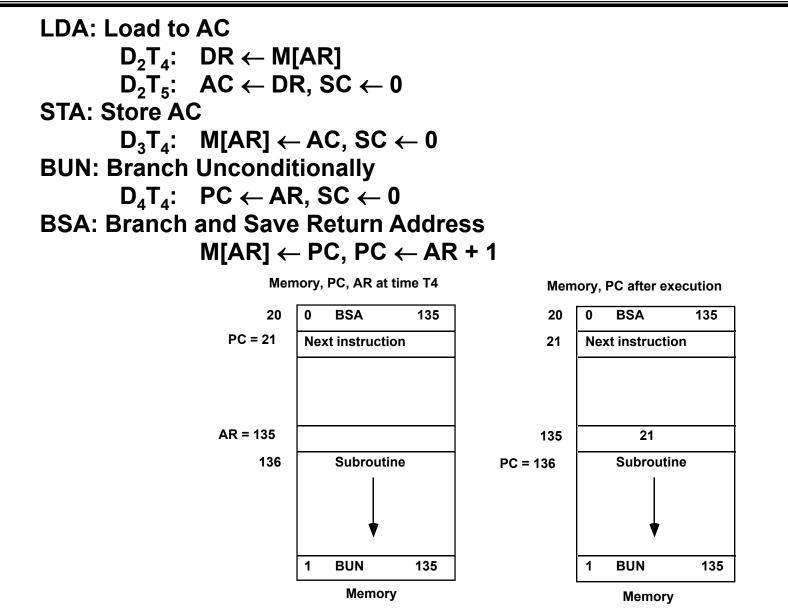

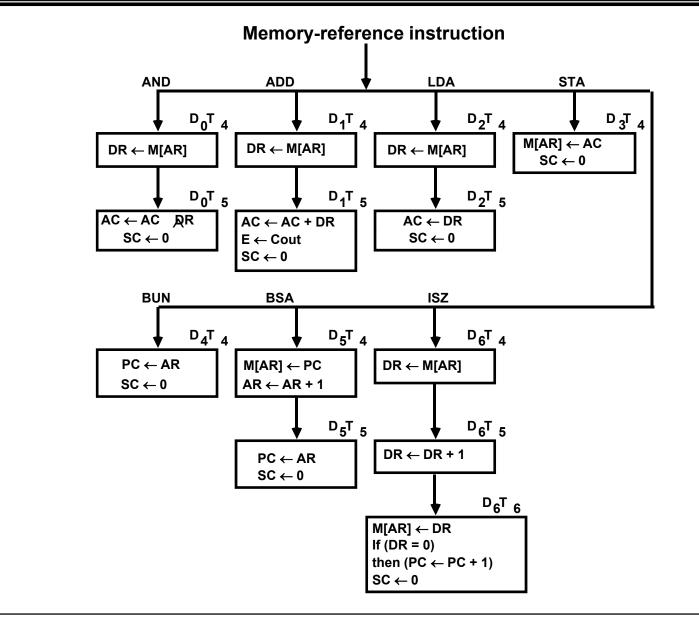

# **MEMORY REFERENCE INSTRUCTIONS**

| Symbol | Operation<br>Decoder | Symbolic Description                                                        |

|--------|----------------------|-----------------------------------------------------------------------------|

| AND    | D <sub>0</sub>       | $AC \leftarrow AC \land M[AR]$                                              |

| ADD    |                      | $AC \leftarrow AC + M[AR], E \leftarrow C_{out}$                            |

| LDA    | $D_2$                | $AC \leftarrow M[AR]$                                                       |

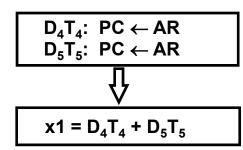

| STA    | $D_3$                | M[AR] ← AC                                                                  |

| BUN    | $D_4$                | PČ ← AR                                                                     |

| BSA    | $D_5$                | $M[AR] \leftarrow PC, PC \leftarrow AR + 1$                                 |

| ISZ    |                      | $M[AR] \leftarrow M[AR] + 1$ , if $M[AR] + 1 = 0$ then PC $\leftarrow$ PC+1 |

- The effective address of the instruction is in AR and was placed there during timing signal T<sub>2</sub> when I = 0, or during timing signal T<sub>3</sub> when I = 1

- Memory cycle is assumed to be short enough to complete in a CPU cycle

- The execution of MR instruction starts with T<sub>4</sub>

### **MEMORY REFERENCE INSTRUCTIONS**

76

**Computer Organization**

# **MEMORY REFERENCE INSTRUCTIONS**

**BSA**:

**ISZ: Increment and Skip-if-Zero**

### **FLOWCHART FOR MEMORY REFERENCE INSTRUCTIONS**

#### Computer Organization

- The flags are needed to synchronize the timing difference between I/O device and the computer

79

**Computer Organization**

**Computer Architecture**

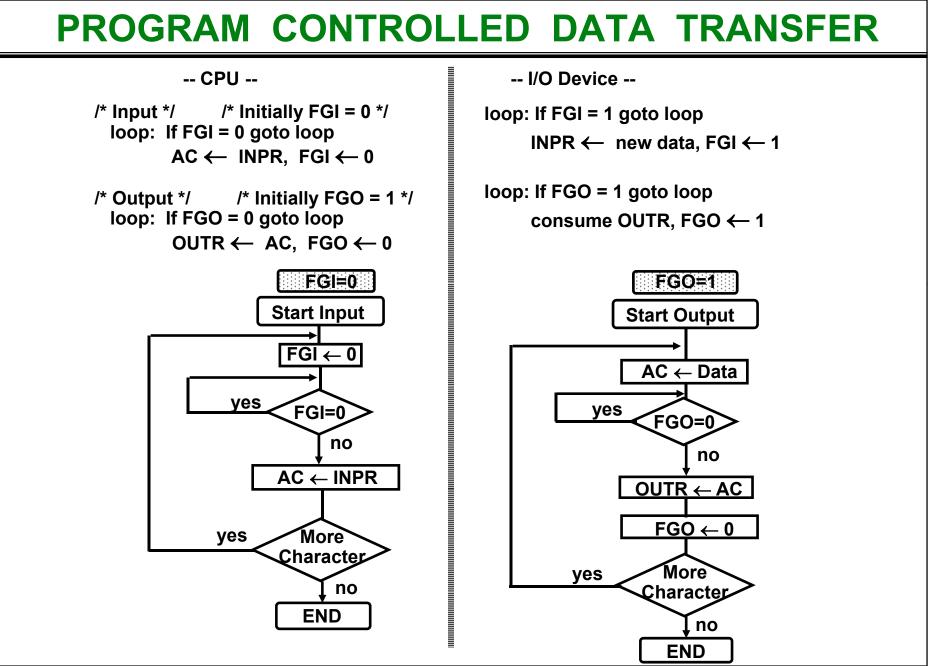

### **PROGRAM-CONTROLLED INPUT/OUTPUT**

- Program-controlled I/O

- Continuous CPU involvement

- I/O takes valuable CPU time

- CPU slowed down to I/O speed

- Simple

- Least hardware

### Input

| LOOP, | SKI | DEV  |

|-------|-----|------|

|       | BUN | LOOP |

|       | INP | DEV  |

### Output

| LOOP, | LDA | DATA |

|-------|-----|------|

| LOP,  | SKO | DEV  |

|       | BUN | LOP  |

|       | OUT | DEV  |

# **INTERRUPT INITIATED INPUT/OUTPUT**

- Open communication only when some data has to be passed --> interrupt.

- The I/O interface, instead of the CPU, monitors the I/O device.

- When the interface founds that the I/O device is ready for data transfer, it generates an interrupt request to the CPU

- Upon detecting an interrupt, the CPU stops momentarily the task it is doing, branches to the service routine to process the data transfer, and then returns to the task it was performing.

- \* IEN (Interrupt-enable flip-flop)

- can be set and cleared by instructions

- when cleared, the computer cannot be interrupted

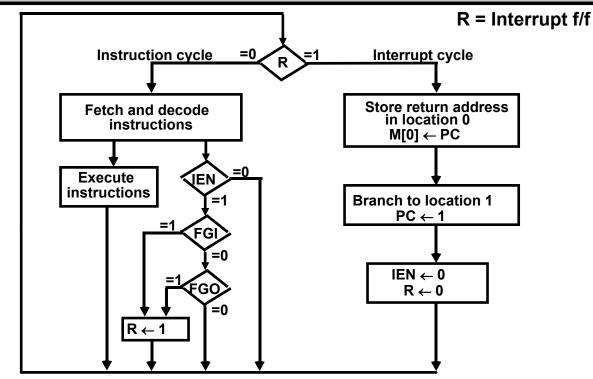

# FLOWCHART FOR INTERRUPT CYCLE

- The interrupt cycle is a HW implementation of a branch and save return address operation.

- At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1.

- At memory address 1, the programmer must store a branch instruction that sends the control to an interrupt service routine

- The instruction that returns the control to the original program is "indirect BUN 0"

# REGISTER TRANSFER OPERATIONS IN INTERRUPT CYCLE Memory

Register Transfer Statements for Interrupt Cycle- R F/F  $\leftarrow$  1if IEN (FGI + FGO)T<sub>0</sub>'T<sub>1</sub>'T<sub>2</sub>' $\Leftrightarrow$  T<sub>0</sub>'T<sub>1</sub>'T<sub>2</sub>' (IEN)(FGI + FGO): R  $\leftarrow$  1

- The fetch and decode phases of the instruction cycle must be modified  $\rightarrow$  Replace T<sub>0</sub>, T<sub>1</sub>, T<sub>2</sub> with R'T<sub>0</sub>, R'T<sub>1</sub>, R'T<sub>2</sub>

- The interrupt cycle :

RT<sub>0</sub>: AR

$$\leftarrow$$

0, TR  $\leftarrow$  PC

RT<sub>1</sub>: M[AR]  $\leftarrow$  TR, PC  $\leftarrow$  0

RT<sub>2</sub>: PC  $\leftarrow$  PC + 1, IEN  $\leftarrow$  0, R  $\leftarrow$  0, SC  $\leftarrow$  0

**Computer Organization**

85

How can the CPU recognize the device requesting an interrupt ?

Since different devices are likely to require different interrupt service routines, how can the CPU obtain the starting address of the appropriate routine in each case ?

Should any device be allowed to interrupt the CPU while another interrupt is being serviced ?

How can the situation be handled when two or more interrupt requests occur simultaneously ?

**Computer Organization**

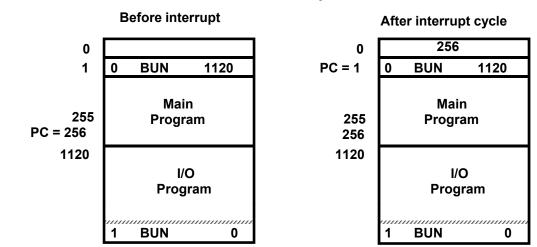

**Basic Computer Organization & Design** 88 Description COMPLETE COMPUTER DESCRIPTION **Microoperations** Fetch AR ← PC R′T₀: R′T₁: IR  $\leftarrow$  M[AR], PC  $\leftarrow$  PC + 1 Decode **R'T**<sub>2</sub>: D0, ..., D7  $\leftarrow$  Decode IR(12 ~ 14),  $AR \leftarrow IR(0 \sim 11), I \leftarrow IR(15)$ Indirect  $AR \leftarrow M[AR]$  $D_7/IT_3$ : Interrupt  $T_0'T_1'T_2'$ (IEN)(FGI + FGO): R ← 1  $AR \leftarrow 0, TR \leftarrow PC$ RT₀: RT₁:  $M[AR] \leftarrow TR, PC \leftarrow 0$  $PC \leftarrow PC + 1$ ,  $IEN \leftarrow 0$ ,  $R \leftarrow 0$ ,  $SC \leftarrow 0$ RT<sub>2</sub>: **Memory-Reference** AND  $DR \leftarrow M[AR]$ D₀T₄:  $AC \leftarrow AC \land DR, SC \leftarrow 0$  $D_0T_5$ : ADD  $D_1T_4$ :  $DR \leftarrow M[AR]$  $AC \leftarrow AC + DR, E \leftarrow C_{out}, SC \leftarrow 0$ **D**<sub>1</sub>**T**<sub>5</sub>: LDA  $D_2T_4$ :  $DR \leftarrow M[AR]$  $AC \leftarrow DR, SC \leftarrow 0$  $D_2T_5$ : STA  $D_{3}T_{4}$ :  $M[AR] \leftarrow AC, SC \leftarrow 0$ BUN  $PC \leftarrow AR, SC \leftarrow 0$  $D_4T_4$ : **BSA**  $M[AR] \leftarrow PC, AR \leftarrow AR + 1$  $D_5T_4$ :  $D_5T_5$ :  $PC \leftarrow AR, SC \leftarrow 0$ ISZ  $D_{6}T_{4}$ :  $DR \leftarrow M[AR]$  $D_6T_5$ :  $DR \leftarrow DR + 1$  $M[AR] \leftarrow DR$ , if (DR=0) then (PC  $\leftarrow$  PC + 1),  $D_6T_6$ : SC ← 0

**Computer Organization**

| Basic Cor | mputer Organizat |                    | 89                                                              | Description |

|-----------|------------------|--------------------|-----------------------------------------------------------------|-------------|

|           | COMP             | LETE               | COMPUTER DESCRIPTION                                            | <b>DN</b>   |

|           |                  |                    | <u>Microoperations</u>                                          |             |

|           |                  |                    |                                                                 |             |

|           | Register-Refer   | ence               |                                                                 |             |

|           |                  | $D_7 l'T_3 = r$    | (Common to all register-reference instr)                        |             |

|           |                  | $IR(i) = B_i$      | (i = 0,1,2,, 11)                                                |             |

|           |                  | r:                 | SC ← 0                                                          |             |

|           | CLA              | rB₁₁:              | AC ← 0                                                          |             |

|           | CLE              | rB <sub>10</sub> : | E ← 0                                                           |             |

|           | CMA              | rB <sub>9</sub> :  | $AC \leftarrow AC'$                                             |             |

|           | CME              | rB <sub>8</sub> :  | E ← E'                                                          |             |

|           | CIR              | rB <sub>7</sub> :  | $AC \leftarrow shr AC, AC(15) \leftarrow E, E \leftarrow AC(0)$ |             |

|           | CIL              | rB <sub>6</sub> :  | $AC \leftarrow shl AC, AC(0) \leftarrow E, E \leftarrow AC(15)$ |             |

|           | INC              | rB₅:               | $AC \leftarrow AC + 1$                                          |             |

|           | SPA              | rB <sub>4</sub> :  | If $(AC(15) = 0)$ then $(PC \leftarrow PC + 1)$                 |             |

|           | SNA              | rB <sub>3</sub> :  | If $(AC(15) = 1)$ then $(PC \leftarrow PC + 1)$                 |             |

|           | SZA              | <b>—</b>           | If (AC = 0) then (PC $\leftarrow$ PC + 1)                       |             |

|           | SZE              | rB₁:               | If(E=0) then (PC ← PC + 1)                                      |             |

|           | HLT              | rB <sub>0</sub> :  | S ← 0                                                           |             |

|           | Input-Output     | $D_7IT_3 = p$      | (Common to all input-output instructions)                       |             |

|           |                  | $IR(i) = B_i$      |                                                                 |             |

|           |                  | p:                 | SC ← 0                                                          |             |

|           | INP              | рВ <sub>11</sub> : | AC(0-7) ← INPR, FGI ← 0                                         |             |

|           | OUT              | pB <sub>10</sub> : | $OUTR \leftarrow AC(0-7), FGO \leftarrow 0$                     |             |

|           | SKI              | pB <sub>9</sub> :  | If(FGI=1) then (PC ← PC + 1)                                    |             |

|           | SKO              | pB <sub>8</sub> :  | If (FGO=1) then (PC $\leftarrow$ PC + 1)                        |             |

|           | ION              | pB <sub>7</sub> :  | IEN ← 1                                                         |             |

|           | IOF              | pB <sub>6</sub> :  | IEN ← 0                                                         |             |

|           |                  |                    |                                                                 |             |

Computer Organization

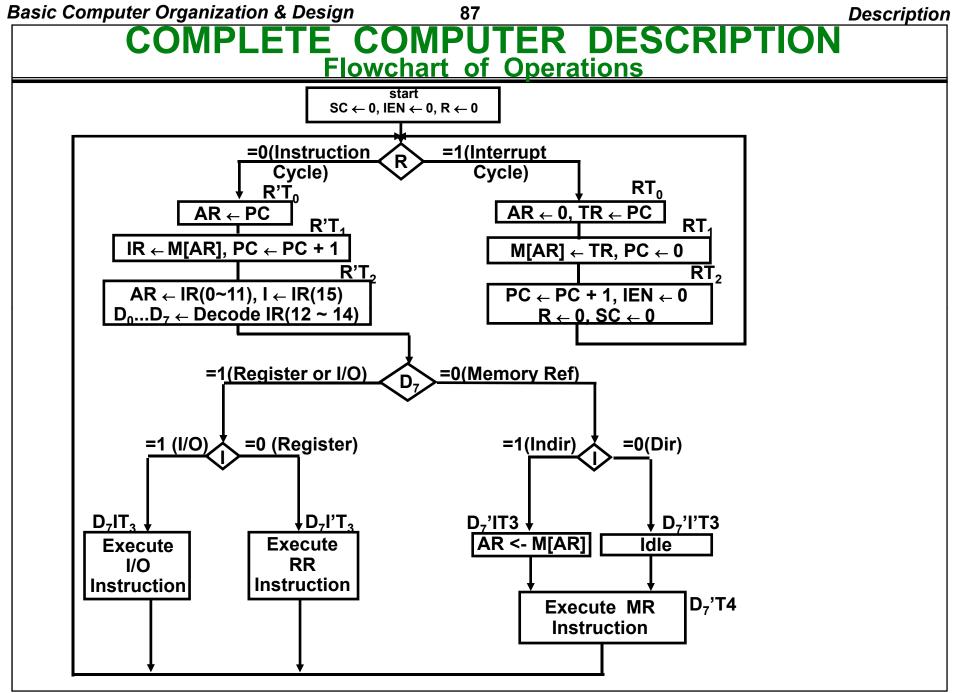

### **DESIGN OF BASIC COMPUTER(BC)**

### Hardware Components of BC

A memory unit: 4096 x 16. Registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC Flip-Flops(Status): I, S, E, R, IEN, FGI, and FGO Decoders: a 3x8 Opcode decoder a 4x16 timing decoder Common bus: 16 bits Control logic gates: Adder and Logic circuit: Connected to AC

**Control Logic Gates**

- Input Controls of the nine registers

- Read and Write Controls of memory

- Set, Clear, or Complement Controls of the flip-flops

- $S_2$ ,  $S_1$ ,  $S_0$  Controls to select a register for the bus

- AC, and Adder and Logic circuit

# **CONTROL OF REGISTERS AND MEMORY**

### Address Register; AR

Scan all of the register transfer statements that change the content of AR:

**Computer Organization**

**Computer Architecture**

91

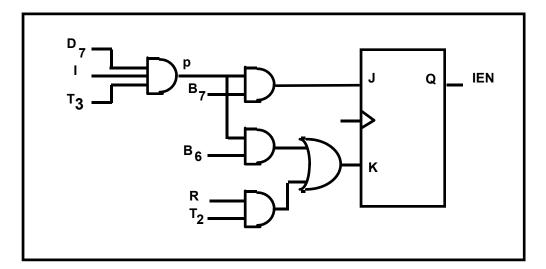

### **CONTROL OF FLAGS**

**IEN: Interrupt Enable Flag**

- pB<sub>7</sub>: IEN  $\leftarrow$  1 (I/O Instruction)

- $pB_6$ : IEN  $\leftarrow 0$  (I/O Instruction)

- **RT**<sub>2</sub>: IEN  $\leftarrow$  0 (Interrupt)

p = D<sub>7</sub>IT<sub>3</sub> (Input/Output Instruction)

Computer Organization

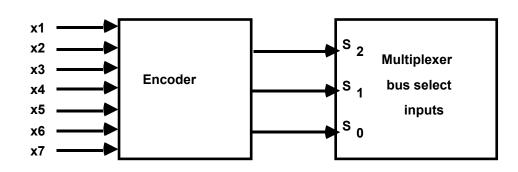

# CONTROL OF COMMON BUS

| x1 | x2 | 2 x | 3) | <b>‹4</b> : | x5 | x6 | x7 | s | 52 S1 | S0   | selected<br>register |

|----|----|-----|----|-------------|----|----|----|---|-------|------|----------------------|

| 0  | 0  | 0   | 0  | 0           | 0  | 0  | 0  | 0 | 0     | none |                      |

| 1  | 0  | 0   | 0  | 0           | 0  | 0  | 0  | 0 | 1     | AR   |                      |

| 0  | 1  | 0   | 0  | 0           | 0  | 0  | 0  | 1 | 0     | PC   |                      |

| 0  | 0  | 1   | 0  | 0           | 0  | 0  | 0  | 1 | 1     | DR   |                      |

| 0  | 0  | 0   | 1  | 0           | 0  | 0  | 1  | 0 | 0     | AC   |                      |

| 0  | 0  | 0   | 0  | 1           | 0  | 0  | 1  | 0 | 1     | IR   |                      |

| 0  | 0  | 0   | 0  | 0           | 1  | 0  | 1  | 1 | 0     | TR   |                      |

| 0  | 0  | 0   | 0  | 0           | 0  | 1  | 1  | 1 | 1     | Memo | ry                   |

|    |    |     |    |             |    |    |    |   |       |      | -                    |

|    |    |     |    |             |    |    |    |   |       |      |                      |

For AR

Computer Organization

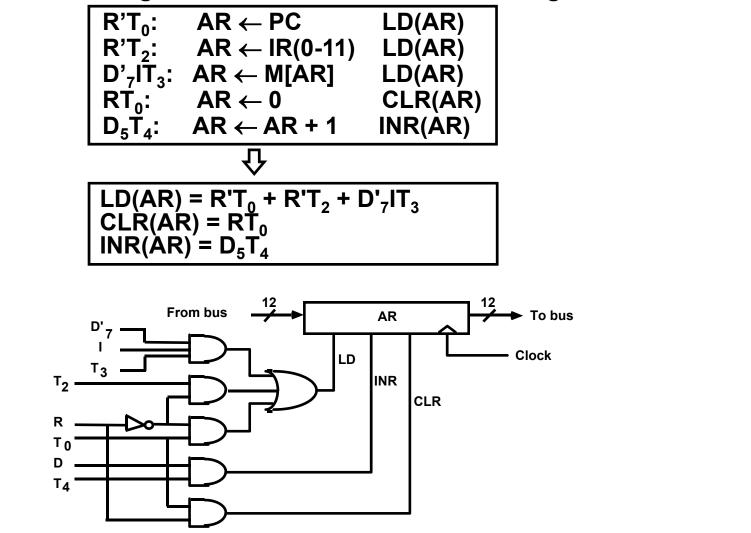

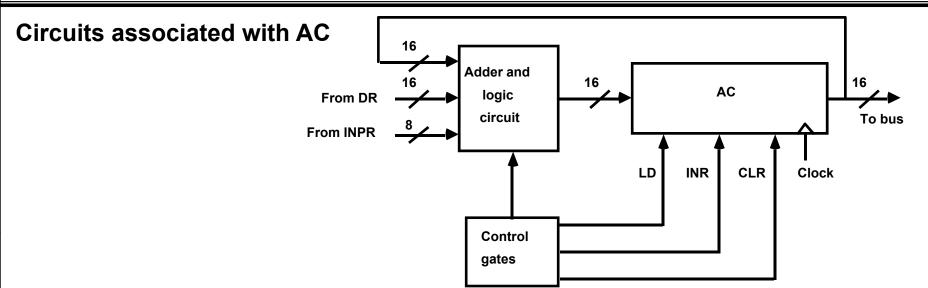

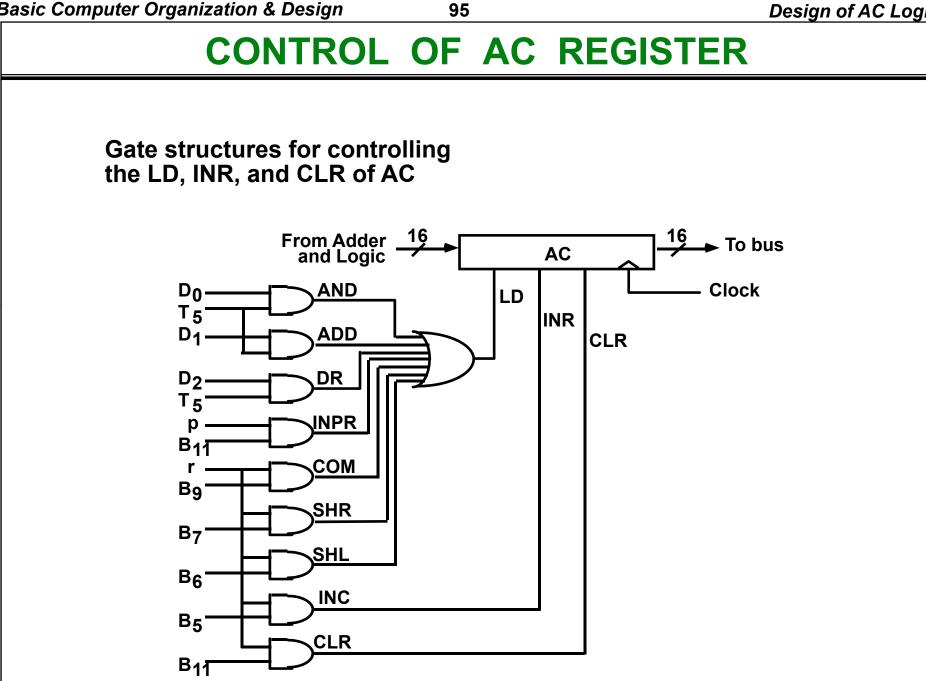

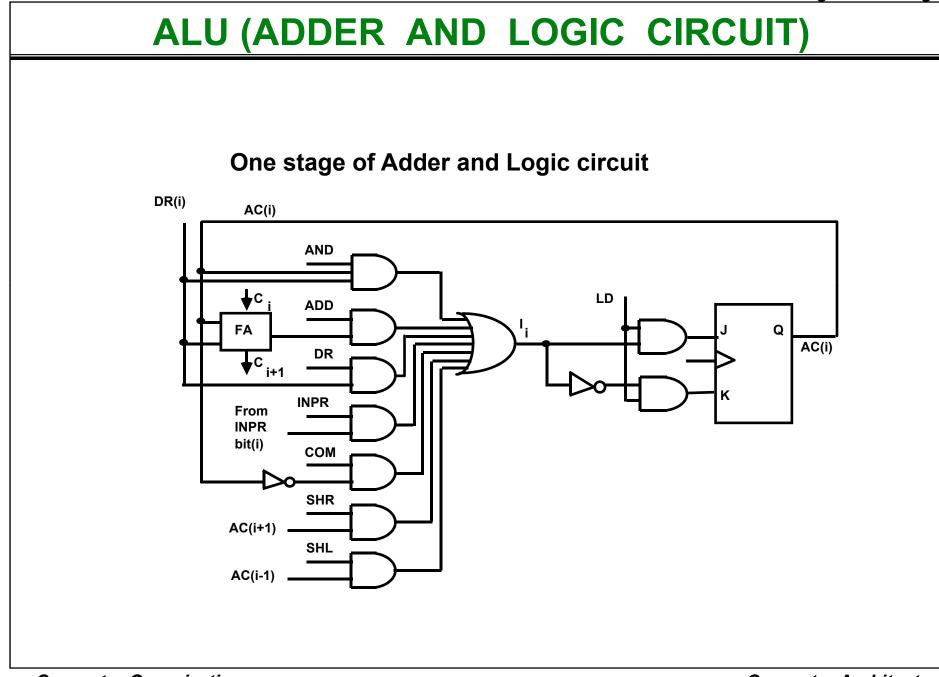

# DESIGN OF ACCUMULATOR LOGIC

### All the statements that change the content of AC

| $D_0T_5$ :                 | $AC \leftarrow AC \land DR$                 | AND with DR        |

|----------------------------|---------------------------------------------|--------------------|

| $D_1 T_5$ :                | $AC \leftarrow AC + DR$                     | Add with DR        |

| $D_{2}T_{5}$ :             | $AC \leftarrow DR$                          | Transfer from DR   |

| pB <sub>11</sub> :         | AC(0-7) ← INPR                              | Transfer from INPR |

| rB <sub>9</sub> :          | $AC \leftarrow AC'$                         | Complement         |

| <b>r</b> B <sub>7</sub> :  | $AC \leftarrow shr AC, AC(15) \leftarrow E$ | Shift right        |

| rB <sub>6</sub> :          | $AC \leftarrow shI AC, AC(0) \leftarrow E$  | Shift left         |

| <b>r</b> B <sub>11</sub> : | $AC \leftarrow 0$                           | Clear              |

| rB <sub>5</sub> :          | $AC \leftarrow AC + 1$                      | Increment          |

| -                          |                                             |                    |

Computer Organization

**Computer Organization**

96

Computer Organization

### INTRODUCTION

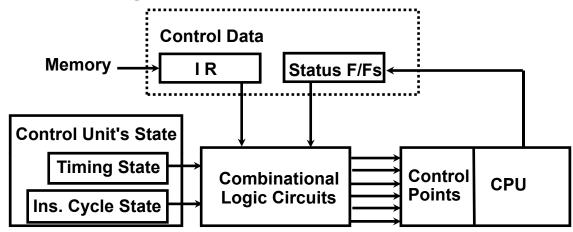

Those concerned with computer architecture should have a knowledge of both hardware and software because the two branches influence each other.

### Instruction Set of the Basic Computer

| Symbol | Hexa cod |                                            |                          |

|--------|----------|--------------------------------------------|--------------------------|

| AND    | 0 or 8   | AND M to AC                                | m: effective address     |

| ADD    | 1 or 9   | Add M to AC, carry to E                    | M: memory word (operand) |

| LDA    | 2 or A   | Load AC from M                             | found at m               |

| STA    | 3 or B   | Store AC in M                              |                          |

| BUN    | 4 or C   | Branch unconditionally to m                |                          |

| BSA    | 5 or D   | Save return address in m and branch to m+1 |                          |

| ISZ    | 6 or E   | Increment M and skip if zero               |                          |

| CLA    | 7800     | Clear AC                                   |                          |

| CLE    | 7400     | Clear E                                    |                          |

| СМА    | 7200     | Complement AC                              |                          |

| CME    | 7100     | Complement E                               |                          |

| CIR    | 7080     | Circulate right E and AC                   |                          |

| CIL    | 7040     | Circulate left E and AC                    |                          |

| INC    | 7020     | Increment AC, carry to E                   |                          |

| SPA    | 7010     | Skip if AC is positive                     |                          |

| SNA    | 7008     | Skip if AC is negative                     |                          |

| SZA    | 7004     | Skip if AC is zero                         |                          |

| SZE    | 7002     | Skip if E is zero                          |                          |

| HLT    | 7001     | Halt computer                              |                          |

| INP    | F800     | Input information and clear flag           |                          |

| OUT    | F400     | Output information and clear flag          |                          |

| SKI    | F200     | Skip if input flag is on                   |                          |

| SKO    | F100     | Skip if output flag is on                  |                          |

| ION    | F080     | Turn interrupt on                          |                          |

| IOF    | F040     | Turn interrupt off                         |                          |

**Computer Organization**

### **MACHINE LANGUAGE**

### • Program

A list of instructions or statements for directing the computer to perform a required data processing task

- Various types of programming languages

- Hierarchy of programming languages

- Machine-language

- Binary code

- Octal or hexadecimal code

- Assembly-language

- Symbolic code

- High-level language

(Assembler)

### (Compiler)

# **COMPARISON OF PROGRAMMING LANGUAGES**

#### Binary Program to Add Two Numbers

| Location | Instruction Code    |

|----------|---------------------|

| 0        | 0010 0000 0000 0100 |

| 1        | 0001 0000 0000 0101 |

| 10       | 0011 0000 0000 0110 |

| 11       | 0111 0000 0000 0001 |

| 100      | 0000 0000 0101 0011 |

| 101      | 1111 1111 1110 1001 |

| 110      | 0000 0000 0000 0000 |

#### Program with Symbolic OP-Code

| Location | า    | Instr | ruction Comments          |

|----------|------|-------|---------------------------|

| 000      | LDA  | 004   | Load 1st operand into AC  |

| 001      | ADD  | 005   | Add 2nd operand to AC     |

| 002      | STA  | 006   | Store sum in location 006 |

| 003      | HLT  |       | Halt computer             |

| 004      | 0053 |       | 1st operand               |

| 005      | FFE9 |       | 2nd operand (negative)    |

| 006      | 0000 |       | Store sum here            |

#### Fortran Program

INTEGER A, B, C DATA A,83 / B,-23 C = A + B END

#### Assembly-Language Program

|          | ORG | 0   | /Origin of program is location 0 |

|----------|-----|-----|----------------------------------|

|          | LDA | Α   | /Load operand from location A    |

|          | ADD | В   | /Add operand from location B     |

|          | STA | С   | /Store sum in location C         |

|          | HLT |     | /Halt computer                   |

| А,       | DEC | 83  | /Decimal operand                 |

| В,       | DEC | -23 | /Decimal operand                 |

| В,<br>С, | DEC | 0   | /Sum stored in location C        |

|          | END |     | /End of symbolic program         |

|          |     |     |                                  |

• Hexa program

| Location | Instruction |

|----------|-------------|

| 000      | 2004        |

| 001      | 1005        |

| 002      | 3006        |

| 003      | 7001        |

| 004      | 0053        |

| 005      | FFE9        |

| 006      | 0000        |

# ASSEMBLY LANGUAGE

Syntax of the BC assembly language

Each line is arranged in three columns called fields *Label* field

- May be empty or may specify a symbolic address consists of up to 3 characters

- Terminated by a comma

Instruction field

- Specifies a machine or a pseudo instruction

- May specify one of

- \* Memory reference instr. (MRI)

- MRI consists of two or three symbols separated by spaces.

- ADD OPR (direct address MRI)

- ADD PTR I (indirect address MRI)

- \* Register reference or input-output instr.

- Non-MRI does not have an address part

- \* Pseudo instr. with or without an operand

- Symbolic address used in the instruction field must be

- defined somewhere as a label

Comment field

- May be empty or may include a comment

### **PSEUDO-INSTRUCTIONS**

ORG N

Hexadecimal number N is the memory loc.

for the instruction or operand listed in the following line

END

Denotes the end of symbolic program

DEC N

Signed decimal number N to be converted to the binary

HEX N

Hexadecimal number N to be converted to the binary

Example: Assembly language program to subtract two numbers

|      | ORG 100<br>LDA SUB | / Origin of program is location 100<br>/ Load subtrahend to AC |

|------|--------------------|----------------------------------------------------------------|

|      | CMA                | / Complement AC                                                |

|      | INC                | / Increment AC                                                 |

|      | ADD MIN            | / Add minuend to AC                                            |

|      | STA DIF            | / Store difference                                             |

|      | HLT                | / Halt computer                                                |

| MIN, | <b>DEC 83</b>      | / Minuend                                                      |

| SUB, | DEC -23            | / Subtrahend                                                   |

| DIF, | HEX 0              | / Difference stored here                                       |

|      | END                | / End of symbolic program                                      |

Computer Organization

# **TRANSLATION TO BINARY**

| Hexadecimal Code |      |                  |               |

|------------------|------|------------------|---------------|

| Location Content |      | Symbolic Program |               |

|                  |      |                  | ORG 100       |

| 100              | 2107 |                  | LDA SUB       |

| 101              | 7200 |                  | СМА           |

| 102              | 7020 |                  | INC           |

| 103              | 1106 |                  | ADD MIN       |

| 104              | 3108 |                  | STA DIF       |

| 105              | 7001 |                  | HLT           |

| 106              | 0053 | MIN,             | <b>DEC 83</b> |

| 107              | FFE9 | SUB,             | DEC -23       |

| 108              | 0000 | DIF,             | HEX 0         |

|                  |      |                  | END           |

**Computer Organization**

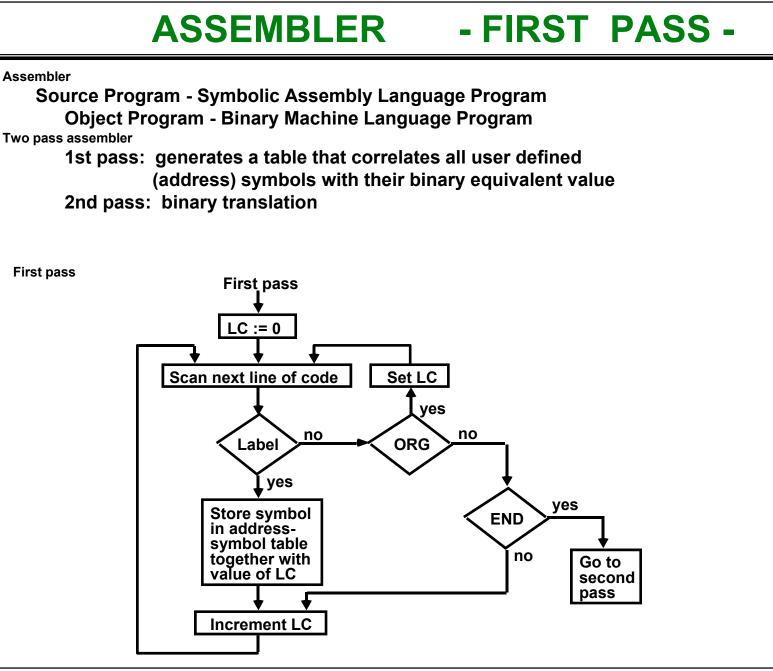

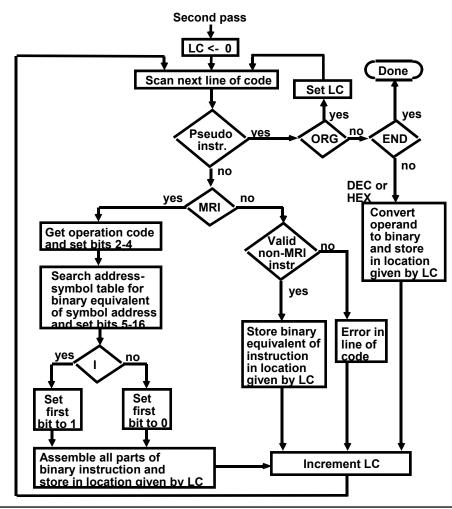

### ASSEMBLER - SECOND PASS -

#### Second Pass

Machine instructions are translated by means of table-lookup procedures;

(1. Pseudo-Instruction Table, 2. MRI Table, 3. Non-MRI Table

4. Address Symbol Table)

**Computer Organization**

### **PROGRAM LOOPS**

3

Loop: A sequence of instructions that are executed many times, each with a different set of data Fortran program to add 100 numbers:

| DIMENSION A(100) |

|------------------|

| INTEGER SUM, A   |

| SUM = 0          |

| DO 3 J = 1, 100  |

| SUM = SUM + A(J) |

Assembly-language program to add 100 numbers:

|      | ORG 100   | / Origin of program is HEX 100  |

|------|-----------|---------------------------------|

|      | LDA ADS   | / Load first address of operand |

|      | STA PTR   | / Store in pointer              |

|      | LDA NBR   | / Load -100                     |

|      | STA CTR   | / Store in counter              |

|      | CLA       | / Clear AC                      |

| LOP, | ADD PTR I | / Add an operand to AC          |

|      | ISZ PTR   | / Increment pointer             |

|      | ISZ CTR   | / Increment counter             |

|      | BUN LOP   | / Repeat loop again             |

|      | STA SUM   | / Store sum                     |

|      | HLT       | / Halt                          |

| ADS, | HEX 150   | / First address of operands     |

| PTR, | HEX 0     | / Reserved for a pointer        |

| NBR, | DEC -100  | / Initial value for a counter   |

| CTR, | HEX 0     | / Reserved for a counter        |

| SUM, | HEX 0     | / Sum is stored here            |

|      | ORG 150   | / Origin of operands is HEX 150 |

|      | DEC 75    | / First operand                 |

|      | :         | •                               |

|      | •         |                                 |

|      | DEC 23    | / Last operand                  |

|      | END       | / End of symbolic program       |

**Computer Organization**

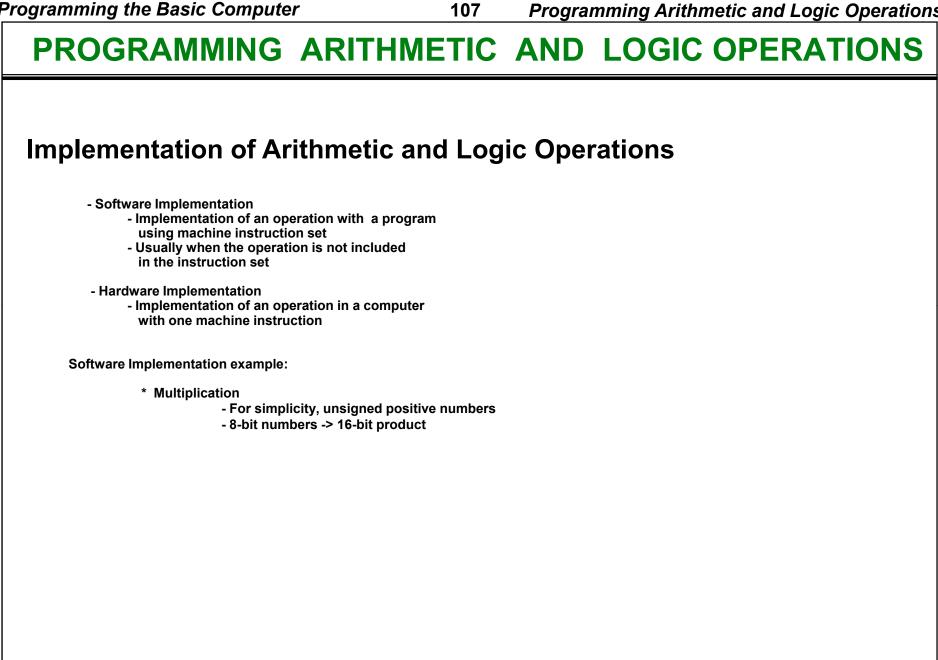

# **FLOWCHART OF A PROGRAM - Multiplication -**

108

**Computer Organization**

### **ASSEMBLY LANGUAGE PROGRAM - Multiplication -**

| LOP,       | ORG 100<br>CLE<br>LDA Y<br>CIR<br>STA Y<br>SZE<br>BUN ONE<br>BUN ZRO | / Clear E<br>/ Load multiplier<br>/ Transfer multiplier bit to E<br>/ Store shifted multiplier<br>/ Check if bit is zero<br>/ Bit is one; goto ONE<br>/ Bit is zero; goto ZRO |

|------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ONE,       | LDA X<br>ADD P<br>STA P<br>CLE                                       | / Load multiplicand<br>/ Add to partial product<br>/ Store partial product<br>/ Clear E                                                                                       |

| ZRO,       | LDA X<br>CIL<br>STA X<br>ISZ CTR<br>BUN LOP<br>HLT                   | / Load multiplicand<br>/ Shift left<br>/ Store shifted multiplicand<br>/ Increment counter<br>/ Counter not zero; repeat loop<br>/ Counter is zero; halt                      |

| CTR,       | DEC -8                                                               | / This location serves as a counter                                                                                                                                           |

| X,<br>  Y, | HEX 000F<br>HEX 000B                                                 | / Multiplicand stored here<br>/ Multiplier stored here                                                                                                                        |

| Р,         | HEX 0<br>END                                                         | / Product formed here                                                                                                                                                         |

| gramming the Basic Computer                   | 111                                                                                                                                                                 | Programm | ing Arithmeti | c and Logic Operati |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|---------------------|

|                                               | BLY LANGUA                                                                                                                                                          |          |               |                     |

| - LO                                          | gic and Shint C                                                                                                                                                     | peralio  | - 51          |                     |

| Logic operations                              |                                                                                                                                                                     |          |               |                     |

| - BC instructions: AND, CMA, CLA              |                                                                                                                                                                     |          |               |                     |

| - Program for OR operation                    |                                                                                                                                                                     |          |               |                     |

| LDA A                                         | / Load 1st operand                                                                                                                                                  |          |               | _                   |

| CMA<br>STA TMP                                | / Complement to get A'<br>/ Store in a temporary loca<br>/ Load 2nd operand B<br>/ Complement to get B'<br>/ AND with A' to get A' ANI<br>/ Complement again to get | tion     |               |                     |

| LDA B<br>CMA                                  | / Load 2nd operand B<br>/ Complement to get B'                                                                                                                      |          |               |                     |

| AND TMP<br>CMA                                | / AND with A' to get A' ANL<br>/ Complement again to get                                                                                                            | A OR B   |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

| Shift operations - BC has Circular Shift only |                                                                                                                                                                     | _        |               |                     |

| - Logical shift-right operation<br>CLE        | - Logical shift-left operation                                                                                                                                      | CLE      | <u> </u>      |                     |

| CIR                                           | C                                                                                                                                                                   | IL       |               |                     |

| - Arithmetic right-shift operation            |                                                                                                                                                                     |          |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

|                                               | Clear E to 0                                                                                                                                                        |          |               |                     |

| CME /                                         | Skip if AC is positive<br>AC is negative                                                                                                                            |          |               |                     |

| CIR /                                         | Circulate E and AC                                                                                                                                                  |          |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

|                                               |                                                                                                                                                                     |          |               |                     |

Computer Organization

### **SUBROUTINES**

#### Subroutine

- A set of common instructions that can be used in a program many times.

- Subroutine *linkage* : a procedure for branching

- to a subroutine and returning to the main program

#### Example

| Loc. |      | ORG 100         | / Main program                     |

|------|------|-----------------|------------------------------------|

| 100  |      | LDA X           | / Load X                           |

| 101  |      | BSA SH4         | / Branch to subroutine             |

| 102  |      | STA X           | / Store shifted number             |

| 103  |      | LDA Y           | / Load Y                           |

| 104  |      | BSA SH4         | / Branch to subroutine again       |

| 105  |      | STA Y           | / Store shifted number             |

| 106  |      | HLT             |                                    |

| 107  | Х,   | HEX 1234        |                                    |

| 108  | Y,   | HEX 4321        |                                    |

|      | ,    |                 | / Subroutine to shift left 4 times |

| 109  | SH4, | HEX 0           | / Store return address here        |

| 10A  | , ,  | CIL             | / Circulate left once              |

| 10B  |      | CIL             |                                    |

| 10C  |      | CIL             |                                    |

| 10D  |      | CIL             | / Circulate left fourth time       |

| 10E  |      | AND MSK         | / Set AC(13-16) to zero            |

| 10F  |      | BUN SH4 I       | / Return to main program           |

| 110  | MSK, | HEX FFF0<br>END | / Mask operand                     |

#### SUBROUTINE PARAMETERS AND DATA LINKAGE

Linkage of Parameters and Data between the Main Program and a Subroutine

- via Registers

- via Memory locations

- ....

#### Example: Subroutine performing LOGICAL OR operation; Need two parameters

| Loc. |      | ORG 200      |                                |

|------|------|--------------|--------------------------------|

| 200  |      | LDA X        | / Load 1st operand into AC     |

| 201  |      | BSA OR       | / Branch to subroutine OR      |

| 202  |      | HEX 3AF6     | / 2nd operand stored here      |

| 203  |      | STA Y        | / Subroutine returns here      |

| 204  |      | HLT          |                                |

| 205  | Χ,   | HEX 7B95     | / 1st operand stored here      |

| 206  | Υ,   | HEX 0        | / Result stored here           |

| 207  | OR,  | HEX 0        | / Subroutine OR                |

| 208  |      | СМА          | / Complement 1st operand       |

| 209  |      | STA TMP      | / Store in temporary location  |

| 20A  |      | LDA OR I     | / Load 2nd operand             |

| 20B  |      | СМА          | / Complement 2nd operand       |

| 20C  |      | AND TMP      | / AND complemented 1st operand |

| 20D  |      | СМА          | / Complement again to get OR   |

| 20E  |      | ISZ OR       | / Increment return address     |

| 20F  |      | BUN OR I     | / Return to main program       |

| 210  | TMP, | HEX 0<br>END | / Temporary storage            |

**Computer Organization**

### **SUBROUTINE - Moving a Block of Data -**

|      |                | / Main program                    |                                  |

|------|----------------|-----------------------------------|----------------------------------|

|      | <b>BSA MVE</b> | / Branch to subroutine            |                                  |

|      | HEX 100        | / 1st address of source data      |                                  |

|      | HEX 200        | / 1st address of destination data |                                  |

|      | DEC -16        | / Number of items to move         |                                  |

|      | HLT            |                                   |                                  |

| MVE, | HEX 0          | / Subroutine MVE                  |                                  |

|      | LDA MVE I      | / Bring address of source         |                                  |

|      | STA PT1        | / Store in 1st pointer            |                                  |

|      | ISZ MVE        | / Increment return address        |                                  |

|      | LDA MVE I      | / Bring address of destination    |                                  |

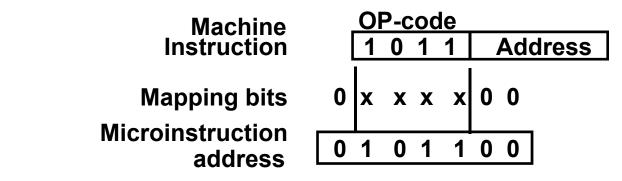

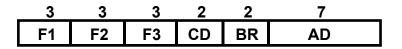

|      | STA PT2        | / Store in 2nd pointer            |                                  |